# **EXILINX**ALL PROGRAMMABLEM

# **IP-XACT extensions for IP interoperability guarantees and software model generation**

Tom Perry<sup>1,2</sup>, Richard Walke<sup>1</sup>, Rob Payne<sup>1</sup>, Stefan Petko<sup>1,2</sup>, Khaled Benkrid<sup>2</sup> <sup>1</sup>Xilinx Scotland <sup>2</sup>ISLI/University of Edinburgh

# Introduction

#### > Contributions:

- IP-XACT extensions

- Software model generation

#### > Outline

- Problem statement

- Proposed solution

- Metadata details

- Results and summary

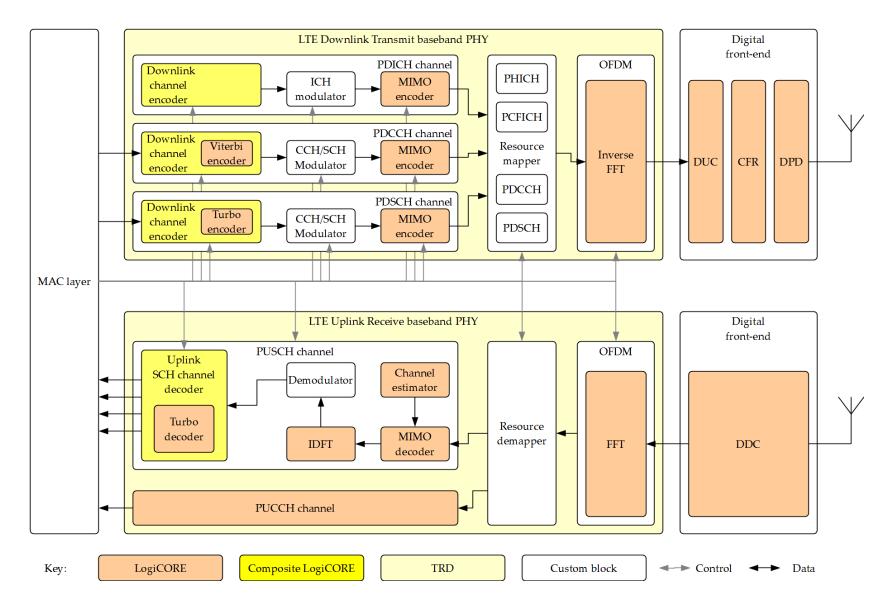

# **Xilinx LTE physical layer systems**

#### XILINX > ALL PROGRAMMABLE.

# LTE design challenges

#### > IP is incompatible at "presentation layer"

- Flag errors?

- Coerce types automatically?

- System is too complex to implement in HDL from scratch: need a model first

- Need to generate test vectors in software which specify required data transactions on hardware block interfaces

- Model development requires time and effort: 16,000 lines of C++

# **State-of-the-art in Xilinx**

- > AXI interfaces on cores "Plug & Play IP" initiative

- > IP-XACT metadata for cores

- Idea: can we use IP-XACT to describe presentation-layer compatibility?

- > Bit-accurate software simulation models for each core

- > Vivado IP Integrator

> Idea: can we use IP Integrator to generate software models?

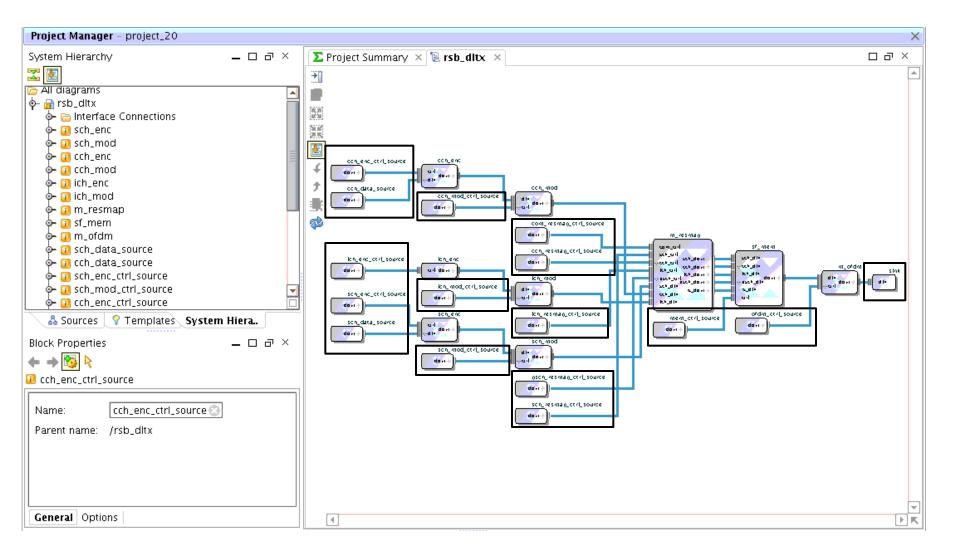

# LTE DL TX system in IP Integrator

#### XILINX > ALL PROGRAMMABLE.

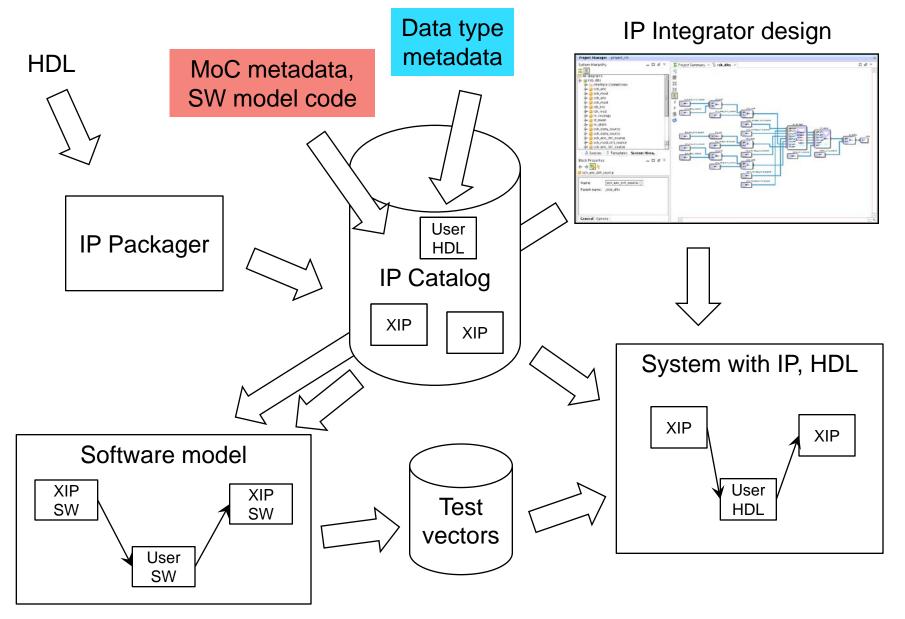

# **Current design flow**

#### IP Integrator design HDL - 0 4 many > 5 reh dits con\_enc\_ont\_source 🗇 User **IP** Packager HDL **IP** Catalog XIP XIP System with IP, HDL XIP XIP > Hard to do system-level architecture User exploration HDL

# **Our modified design flow**

XILINX > ALL PROGRAMMABLE.

# **Metadata extensions**

#### > Aim: extend the IP-XACT metamodel to capture additional aspects of Xilinx IP cores

#### > Data type metadata is needed for two purposes:

- Checking IP compatibility

- Specifying test vector encoding

#### > Model of computation metadata is also useful:

- Can associate software processing with "actions"

- Can ensure that latency-sensitive IP cores are not instantiated into a variable-latency system (not discussed in detail here)

# Data type storage

<spirit:port>

<spirit:vendorExtensions>

<x:dataType>

```

</x:dataType>

</spirit:vendorExtensions>

</spirit:port>

```

```

<spirit:port>

<spirit:vendorExtensions>

<x:dataTypeRef

spirit:vendor="example.com"

spirit:library="lte"

spirit:name="resource_block"

spirit:version="1.0" />

</spirit:vendorExtensions>

</spirit:port>

```

Type description added to a port

Type description stored externally and referenced

# Leaf types

```

<x:dataType>

<x:bitWidth>5</x:bitWidth>

<x:signed/>

<x:real>

<x:fractionalWidth>4</x:fractionalWidth>

</x:real>

</x:real>

```

#### 5-bit signed fixed-point type with 4-bit fractional part

- Must distinguish width of type from width of container, e.g. 8-bit bus

- If <x:bitWidth> not present, type occupies the full size of the container

- > Similar approach for integers, bools, floats

- > Complex type is a pair of integers or reals

# **Hierarchical types**

```

<x:dataType>

<x:structure>

<spirit:field>

<spirit:name>first</spirit:name>

<spirit:bitWidth>...</spirit:bitWidth>

<spirit:bitOffset>...</spirit:bitOffset>

<spirit:vendorExtensions>

<x:dataType>

...

> Structure

```

```

</r> </x:dataType>

</spirit:vendorExtensions>

</spirit:field>

...

</spirit:field>

...

</spirit:field>

...

</x:structure>

</x:dataType>

```

# Reuses <spirit:field> element from IP-XACT register definitions

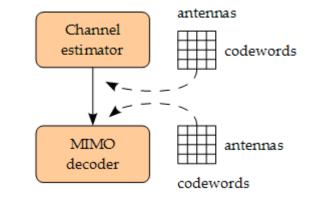

# **Hierarchical types**

```

<x:dataType>

<x:array>

<x:name>antennas</x:name>

<x:size>4</x:size>

<x:dataType>

<x:array>

<x:name>codewords</x:name>

<x:size>4</x:size>

<x:dataType>

. . .

</x:dataType>

</x:array>

</x:dataType>

</x:array>

</x:dataType>

```

#### > Hierarchical array

- Dimensions are named, allowing incompatible orderings to be detected or corrected

- Each dimension has a size

- Dimensions may have a stride…

# **Parameterisable types**

- > Need to handle types that change depending on core parameters

- In the DUC/DDC LogiCORE, this can be done with variable stride lengths

| TDM: false, NANT: 2 |      |      |      |      | TDM: true, NANT: 4 |                |      |      |      |      |

|---------------------|------|------|------|------|--------------------|----------------|------|------|------|------|

| 64                  | 48   | 32   | 16   | 0    |                    | 64             | 48   | 32   | 16   | 0    |

| t <sub>o</sub>      | Q0A2 | 10A2 | Q0A1 | 10A1 |                    | t <sub>o</sub> | 10A4 | 10A3 | 10A2 | 10A1 |

|                     |      |      |      |      | 1                  |                |      |      |      |      |

| t_1                 | Q1A2 | I1A2 | Q1A1 | I1A1 |                    | t              | Q0A4 | Q0A3 | Q0A2 | Q0A1 |

|                     |      |      |      |      | 1                  |                |      |      | 1    |      |

| t <sub>2</sub>      | Q2A2 | 12A2 | Q2A1 | I2A1 |                    | t <sub>2</sub> | I1A4 | I1A3 | I1A2 | I1A1 |

|                     |      |      |      |      |                    |                |      |      |      |      |

| t <sub>3</sub>      | Q3A2 | I3A2 | Q3A1 | I3A1 |                    | t <sub>3</sub> | Q1A4 | Q1A3 | Q1A2 | Q1A1 |

|                     |      |      | ļ    |      |                    |                |      |      |      | I    |

| t                   | T    |      |      | ļ    |                    | t              |      |      |      |      |

```

<x:dataType>

<spirit:parameters>

<spirit:parameter>

<spirit:name>TDM</spirit:name>

<spirit:value

spirit:format="integer"

spirit:id="TDM" />

</spirit:parameter>

... [same for NANT and D_WIDTH]

</spirit:parameters>

<x:array>

<x:name>antennas</x:name>

<x:size spirit:dependency="id('NANT')"/>

<x:stride spirit:dependency=

"if(id('TDM')) then id('D_WIDTH')

else id('D_WIDTH') * 2"/>

<x:dataType>

<x:complex>

<x:real>

<x:bitWidth spirit:dependency=

"id('D_WIDTH')"/>

</x:real>

<x:realInLSBs/>

<x:stride spirit:dependency=

"if(id('TDM'))

then id('D_WIDTH') * id('NANT')

else id('D_WIDTH')"/>

</x:complex>

</x:dataType>

</x:array>

</x:dataType>

```

# **Dataflow action metadata**

- Each component can be described as an actor with "actions" in CAL language

- C++ processing functions can be scheduled using action metadata

- For Xilinx bit-accurate IP simulation models, we reference [wrapped] software entry point in metadata

### Results

- Data type and MoC metadata can be used to assist in the generation of a software simulation model which outputs encoded test vectors

- > Original software models: 16,000 lines of C++ code.

- New models: 3,000 lines of DSL (data types, CAL/NL dataflow) generating 18,000 lines of C++, and 4,000 lines of C++ 'action functions' created manually.

- Total code requirement reduced by >50%, C++ requirement reduced by ~75%.

# **Final comments**

#### Data type extensions documented as an IP-XACT "PSS"

#### Limitations

- Highly dynamic types, e.g. IP optional headers

- Specification of dynamic array sizes

- Differences between XIP software models  $\rightarrow$  need to add wrappers

#### > Ongoing work

- Descriptions of data types in IP Packager (Andrew Dow, Xilinx Edin.)

- Generation of heterogeneous software/hardware systems

- Mapping components to software (simulation model) or hardware

- > More information available from Stefan and I

- Happy to answer any questions