A Graphical Tool for the Generation of Configuration **Bitstreams for a Smart Sensor Interface Based on Coarse-Grained Dynamically Reconfigurable Hardware**

**FPL2012**

22nd International Conference on Field Programmable Logic and Applications

**François Philipp and Manfred Glesner Microelectronic Systems Research Group** Merckstraße 25, 64283 Darmstadt, Germany {francoisp,glesner}@mes.tu-darmstadt.de

(GECO)<sup>2</sup> Dynamic Configuration Editor

## **Motivation**

Rapid development of hardware accelerators

Sensors (ADC, Digital Sensor, ...)

File Action Abou

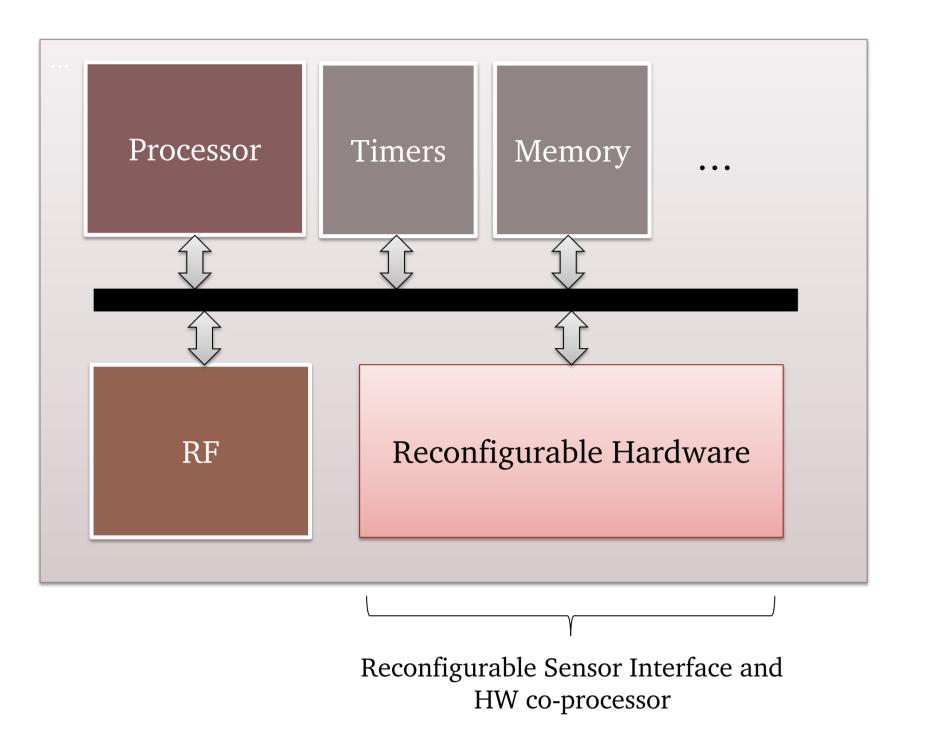

#### for autonomous wireless smart sensor devices :

Suitable for energy efficient acceleration of computationnally demanding tasks in WSNs :

- Sensor data preprocessing

- Feature Exctraction

- Encryption / FEC

Configurable  $S_2$ SRAM Flash sensor interfaces Access Access Configuration Library FIFO FIFO FIFO 25 V Config Processor V Managei Global RAM FIFO Heterogeneous Config. Coarse-Grained Manager Local Reconfigurable Config Datapath Manager RAM Main system Access

### <u>Requirements :</u>

- Flexibility : each sensor network application has different sensors / processing algorithms

- Performance

- **Programmability:** WSN developpers are

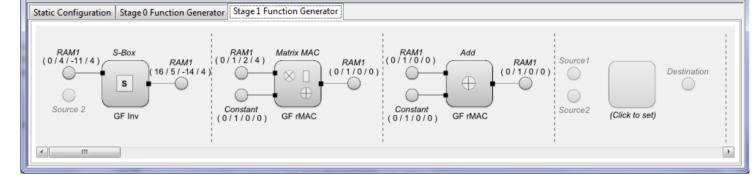

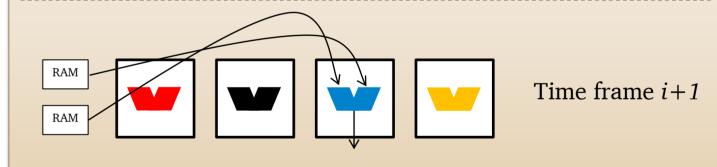

AES encryption round configuration

Fixed Point Radix 2 FFT configuration

- Graphical elaboration of data flows through  $\bullet$ reconfigurable operators

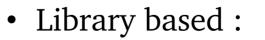

- Stream-based

- Sequential overview

- Editor for compilable microprogram to edit control flow of frames

- Automatically generate configuration bitstream compatible with static architecture defined in step (1)

$\bullet$

#### not familiar with programmable logic design

<u>**G**</u>raphical <u>**E**</u>nvironment for <u>**Co**</u>nfiguration and <u>Generation of bitstreams of Coarse-grained</u> dynamically reconfigurable architectures

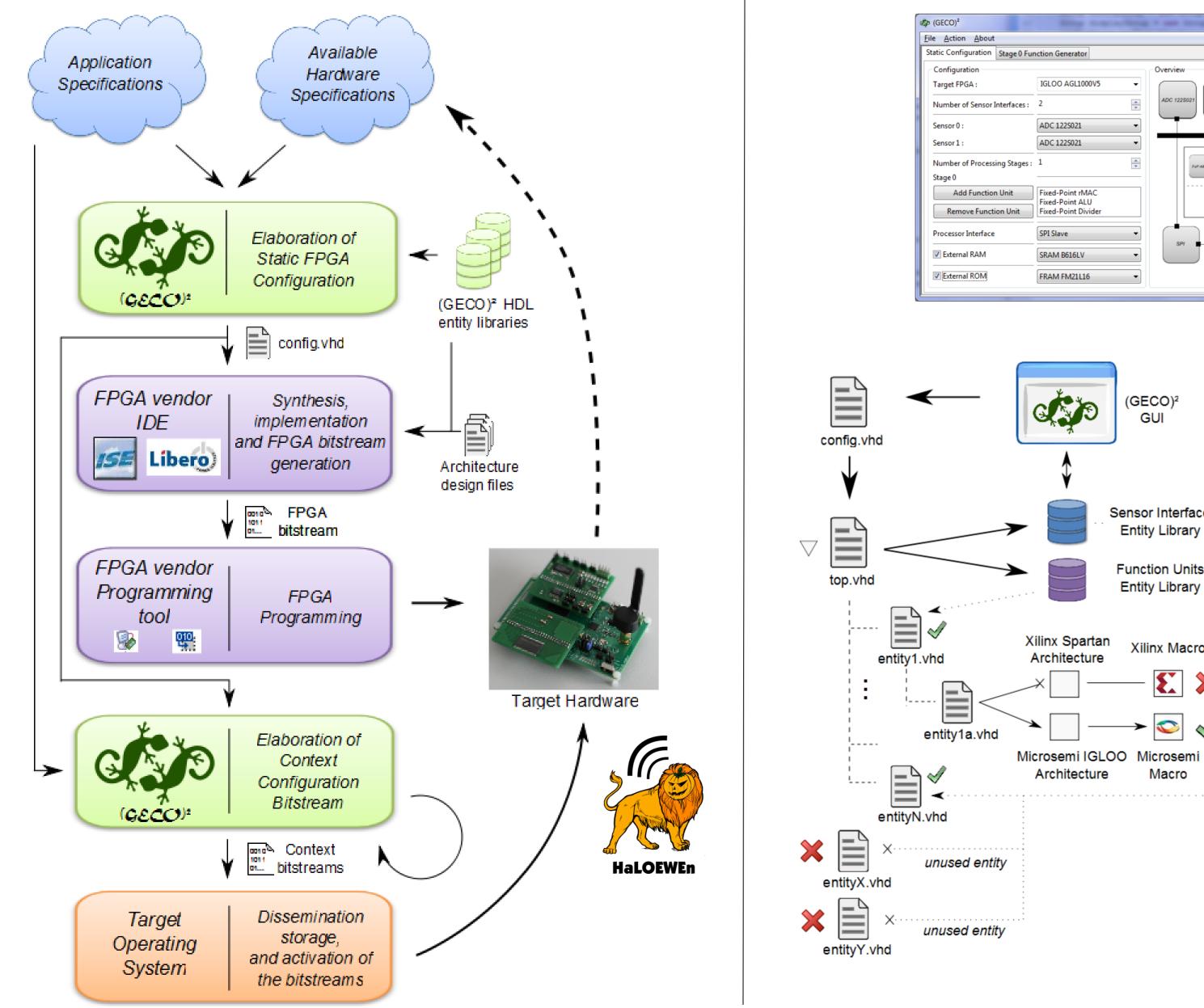

## (GECO)<sup>2</sup> Design Flow

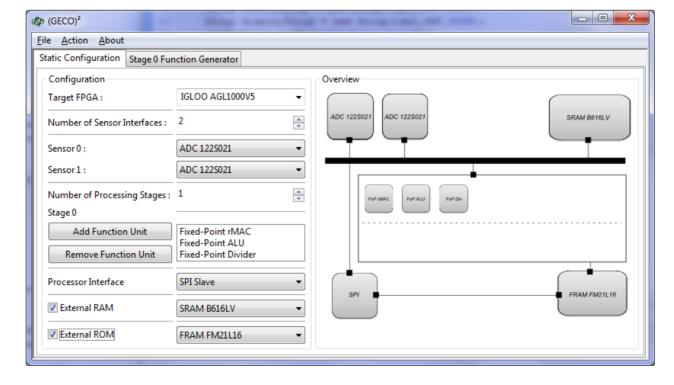

#### . Static Configuration

• Application specific customization of datapath reconfigurable operators • Selection of HW sensor interfaces

2. Elaboration of dynamically loadable configurations corresponding to the static architecture

• Time-multiplexed streaming processes

# (GECO)<sup>2</sup> Static Design

Sensor Interface

Entity Library

Function Units

Entity Library

Xilinx Macro

Macro

**E** 🗙

Xilinx Spartan

Architecture

## RAM 🧲

- Sequences can be saved as function macro for further reuse

- Macro can be dynamically loaded on remote sensor node with compatible architecture

## (GECO)<sup>2</sup> Usage

#### Macro View of a ZOOM FFT algorithm

• Circled numbers indicate the sequence of macros dynamically configured in the datapath

- compatible sensor interfaces and operators can be selected for the design

- Multiple configurable processing stages : Domain-specific operators

- Automatic generation of VHDL top level entities

- Support multiple FPGA vendors specific macros

- Rapid elaboration of high performance data processing HW accelerators enabled

- Suitable for low power high-bandwidth sensing devices

### Acknowledgments

This work has been supported by the European project Maintenance on Demand (MoDe) Grant FP7-SST-2008-RTD 233890 and LOEWE-Project AdRIA

TU Darmstadt | FB18 Elektrotechnik und Informationstechnik | Microelectronic Systems Research Group | F. Philipp and M. Glesner, FPL2012, A Graphical Tool for the Generation of Configuration Bitstreams for a Smart Sensor Interface Based on Coarse-Grained Dynamically Reconfigurable Hardware