# **EXILINX**ALL PROGRAMMABLE

# Beyond Moore. Beyond Programmable Logic.

# **Steve Trimberger**

Xilinx Research FPL 30 August 2012

© Copyright 2012 Xilinx

# Beyond Moore. Beyond Programmable Logic.

© Copyright 2012 Xilinx

# Agenda

#### > What is happening in semiconductor technology?

- Moore's Law

- More than Moore

- Less than Moore?

#### > What is happening at Xilinx?

- How Xilinx is dealing with the latest in semiconductor technology

- Technology and product trends

- The latest round of devices and technologies

- It is not just logic anymore

- > What will happen next?

## Part 1. Is Moore's Law Ending?

## Part 1. Is Moore's Law Ending?

# Railroad Track 1820-1890

Goetz, Transvision 8/2004

Miles (thousands)

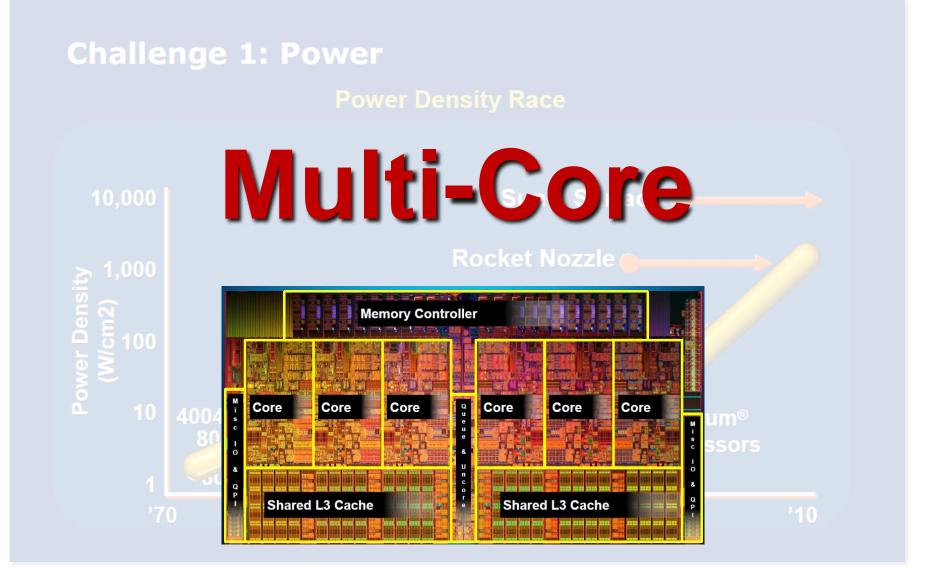

# **Nothing New: Power Challenge**

Source: Intel

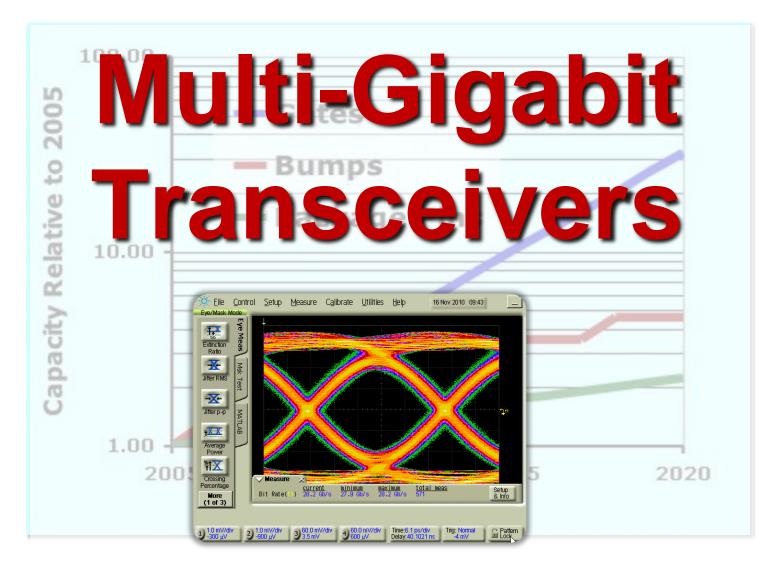

# Nothing New: I/O Bandwidth Gap

Source: Xilinx, Inc.

# **Nothing New: Productivity Gap**

Source: SEMATECH

Page 8

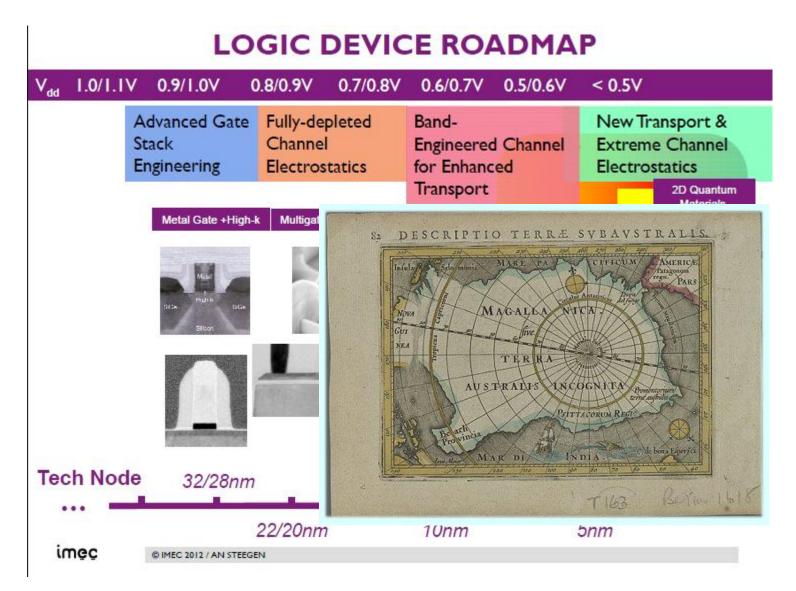

# Moore's Law: The Technology Pipeline

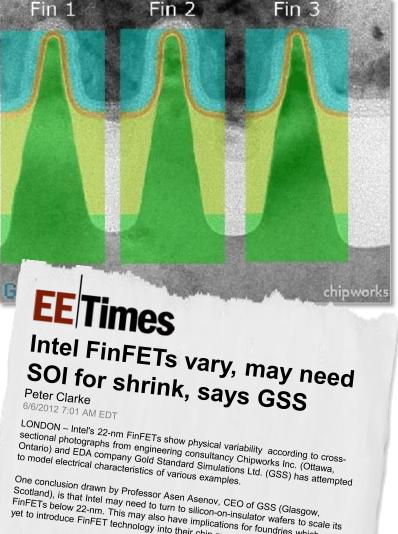

# **Industry Debates Variability and Reliability**

FinFETs below 22-nm. This may also have implications for foundries which are yet to introduce FinFET technology into their chip manufacturing processes.

#### **EE**Times IMEC looks at variability beyond 10 nm Anne-Françoise PELE

6/1/2012 5:10 PM EDT

PARIS – CMOS technology scaling will go on for the foreseeable future

but, as we enter the 10nm node, process complexity reduction and variability control will become crucial and drive technology decisions, said An Steegen, senior vice president process technology at Imec, at the annual IMEC Technology Forum last week at the Square meeting center in Brussels, Belgium.

#### VARIABILITY IMPACT 14nm BULK FINFET CASE

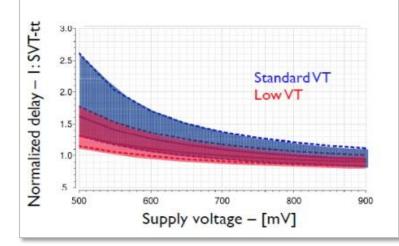

# **Industry Debates Cost**

# Moore's Law Today

- > We still get more transistors!

- Must trade performance for power savings

- Dennard scaling ended around 2000

- Slow growth of I/O pins

- I/O bandwidth requirements drive high-speed serial

- Less area improvement with each new node

- Lithography limitations restrict layout

- Quantized transistor sizes with FinFETs

- Process complexity and limited suppliers drive up wafer pricing and delay production price reductions

- > We still get more transistors!

# **Part 2. What Is Xilinx Doing?**

# Expanding Programmable Technology Leadership

- **Committed to be First to Process Nodes**

- > Pioneering 3-D IC Technology

- >Leading Edge Processing Systems

- > Programmable Analog/Mixed Signal

- >System to IC Tools, IP, and Ecosystem

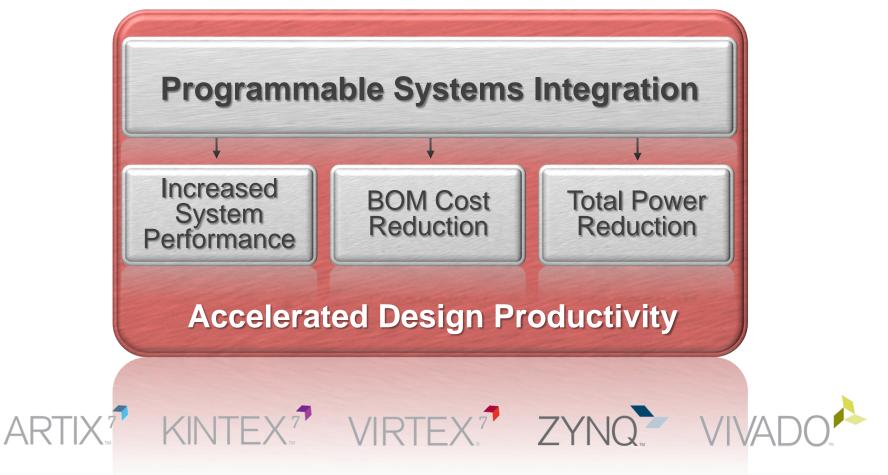

# From Programmable Logic to Programmable Systems Integration

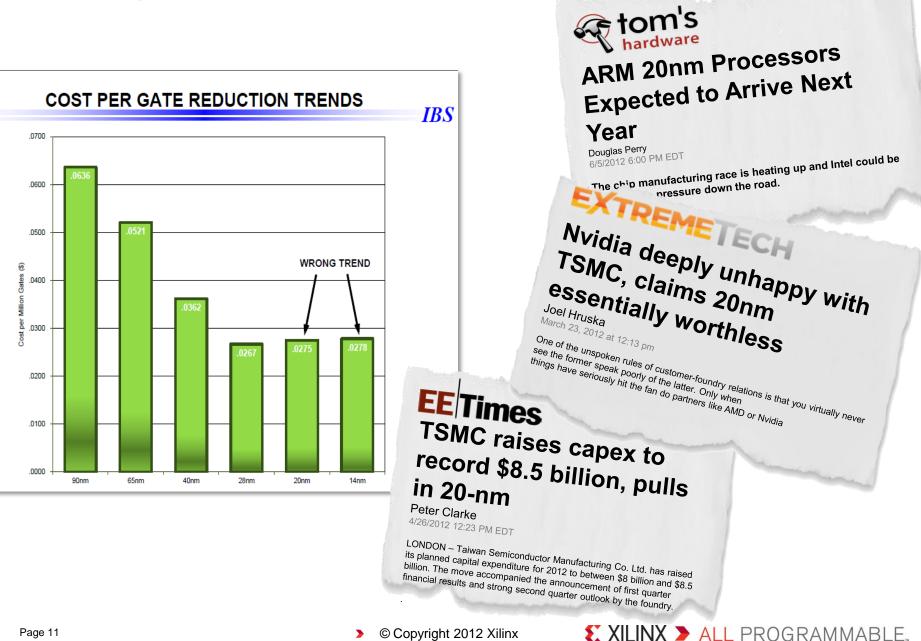

# **FPGA Capacity Trend Looking Up**

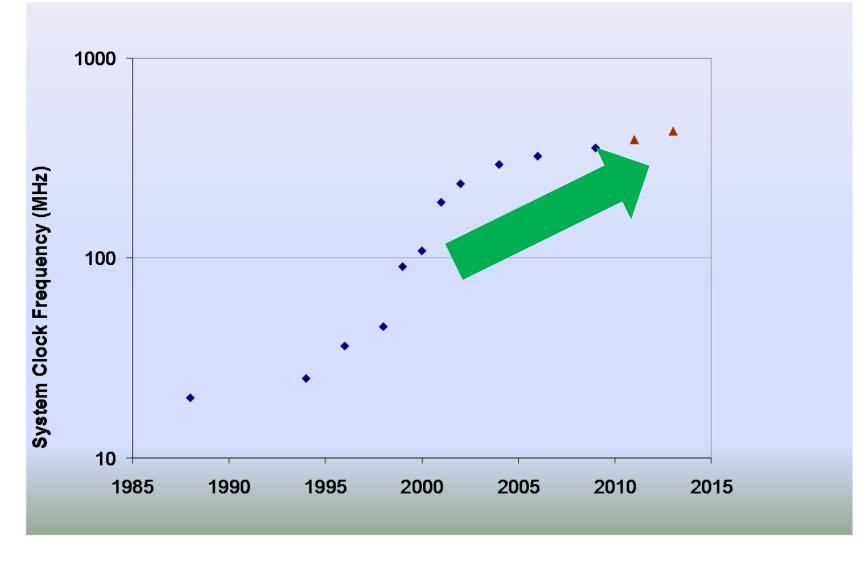

# FPGA Performance Trend Looking Up

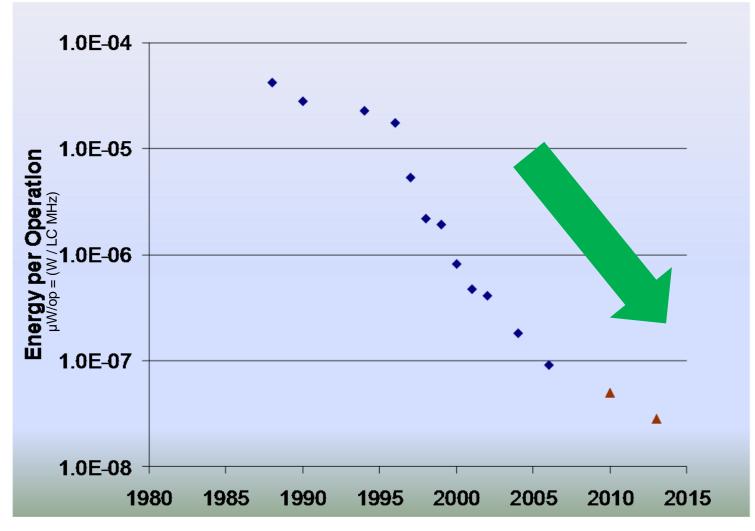

# FPGA Energy Trend Looking d

© Copyright 2012 Xilinx

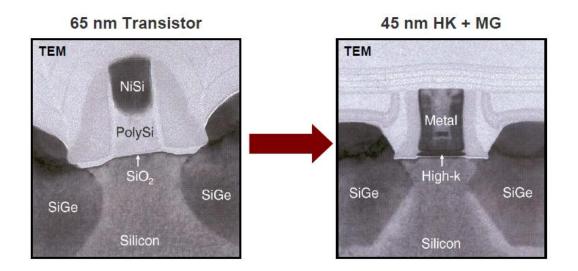

# High-k Metal Gate Transistor in 28nm HPL Process

#### HKMG: - introduced by Intel at 45nm - available at 28nm from top foundries

> 25x lower gate oxide leakage

- > 30% lower switching power

- > 30% higher drive current or

- > 5x lower source-drain leakage

Source: "Challenges and Innovations in Nano-CMOS Transistor Scaling", Tahir Ghani, Intel, Oct 2009

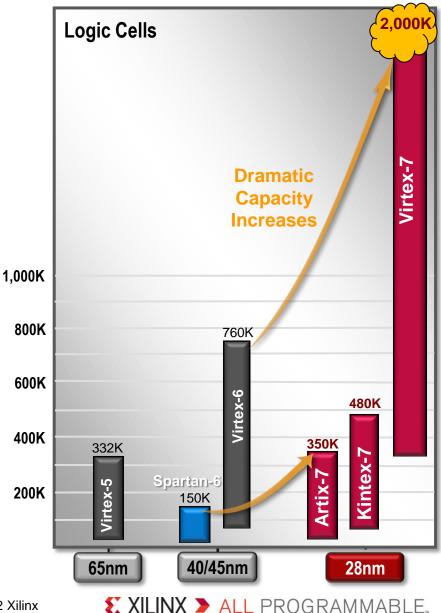

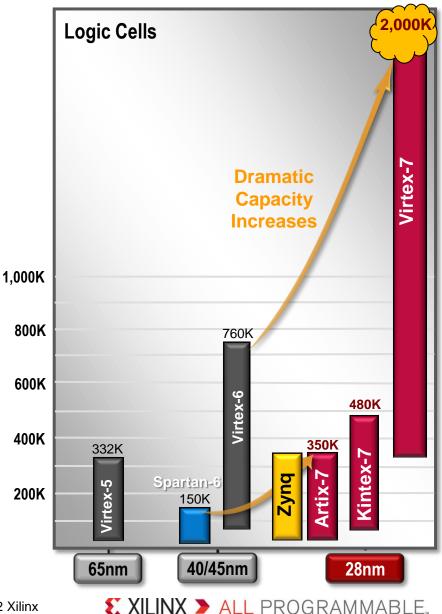

### Ground Breaking Capacity Gains at 28nm World's First 2 Million Logic Cell FPGA

> Over 2x capacity increase over Spartan-6 and Virtex-6 FPGAs

| Family               | Capacity Range        |  |

|----------------------|-----------------------|--|

| ARTIX.7              | 8K – <b>350K LCs</b>  |  |

| KINTEX. <sup>7</sup> | 70K – <b>480K LCs</b> |  |

| VIRTEX.7             | 330K – <b>2M LCs</b>  |  |

- SK 2M LCs; the widest capacity range offered in a single unified product family

- Larger densities enable higher performance

- More calculations/clock cycle by utilizing

Page parallelism inherent in FPGAs © Copyright 2012 Xilinx

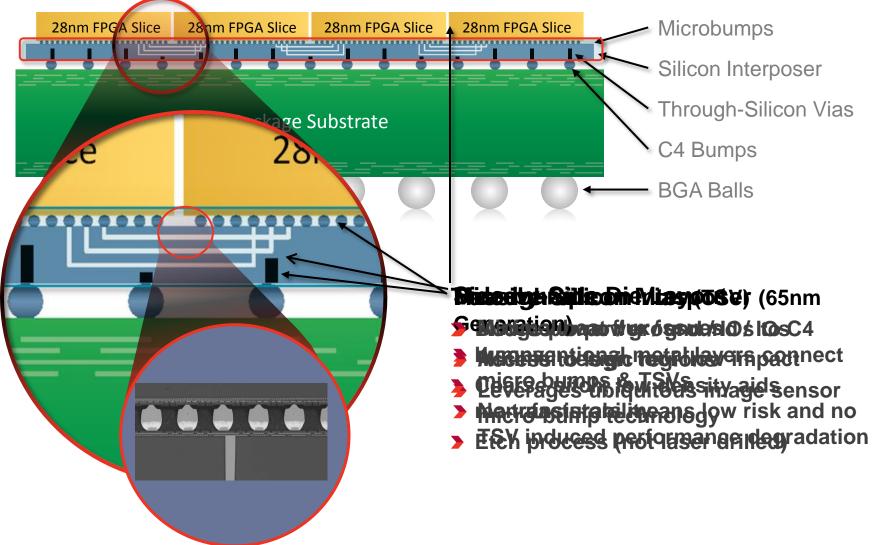

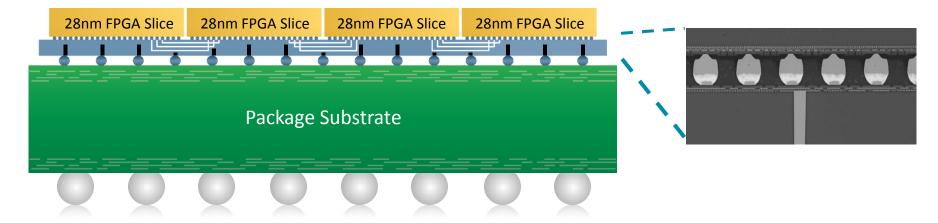

# SSI Technology Harnesses Proven Technology in a Unique Way

Page 20

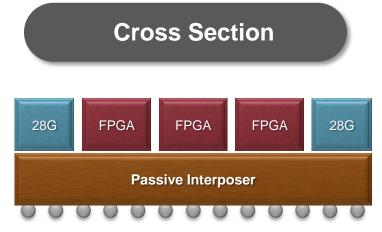

# 2.5D: Crossing the Chasm

# Virtex 2000T: Homogeneous 3D

----

- > 4-layer metal Si interposer with TSV

- > 4 FPGA sub-die in package

- >>10,000 inter-die connections

- > 2 Million Logic Cells

- > 6.8 *Billion* Transistors

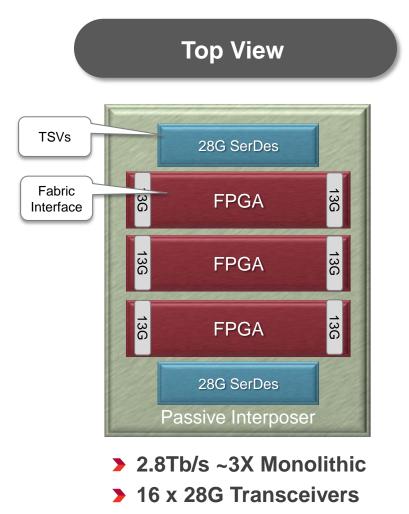

# Virtex-7 HT: Heterogeneous 3D

- > 72 x 13G Transceivers

- > 650 GPIO

- Yield optimized

- Noise isolation

- > 28G transceiver process optimized for performance

- > FPGA logic process optimized for

power

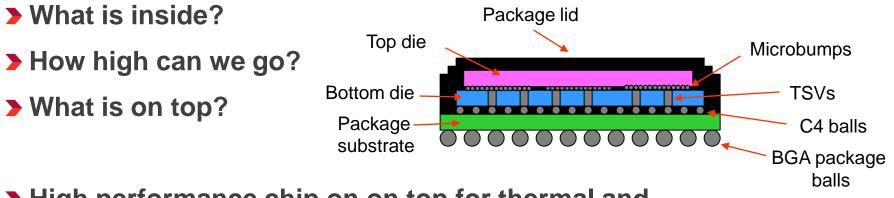

# **3D: The Next Frontier**

- > High performance chip on on top for thermal and TSV process availability

- Bottom die supports power TSV's for top die (Swiss cheese) in older technology (TSV friendly)

- > Floor-planning critical:

- Thermal concerns (stacked thermal flux)

- TSV keep out zones in bottom die to avoid stressinduced performance impact

- What about user-defined stacks?

TSV-Induced Device Stress

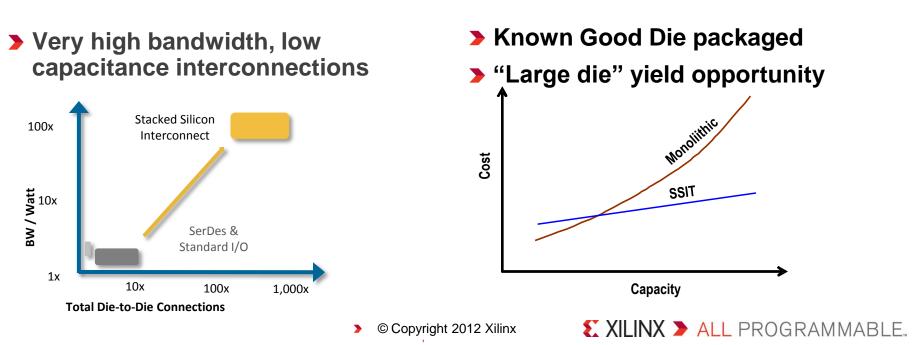

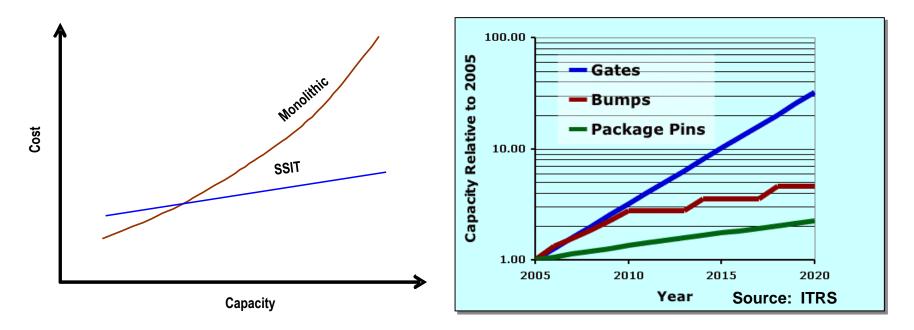

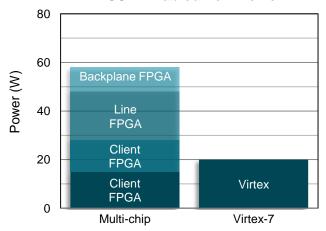

# **Beyond Moore with SSIT**

- > Break the exponential cost of large die

- Break through pin limitations for higher bandwidth and lower power

- > No more compromises for high-performance vs. low power for very high-speed I/O

# **Nothing New: Productivity Gap**

Source: SEMATECH

# Hardware and Software Programmability

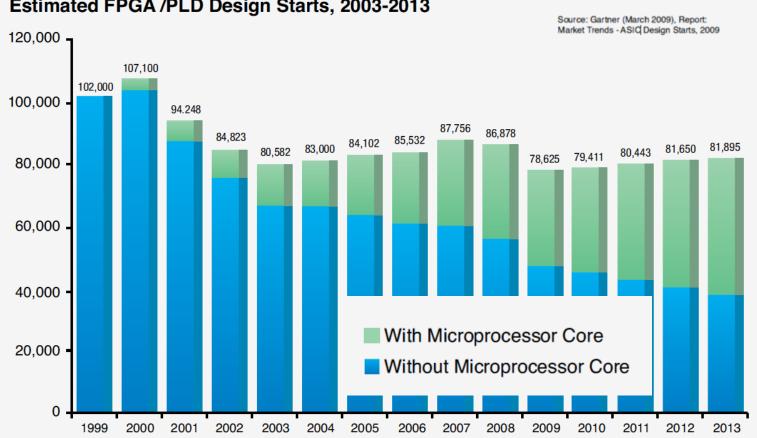

Estimated FPGA /PLD Design Starts, 2003-2013

# **Xilinx Technology Evolution**

Logic

FPGA

**ALL Programmable Devices Enables Programmable** Systems 'Integration'

AMBA

PGA

Algorithms

3D-1C

ARM FPGA

SerDe

MP

Logic

all 3DIC

SoC

FPGA

MS

Protocols

SerDes

AMS

AMS

XILINX > ALL PROGRAMMABLE.

SW

10

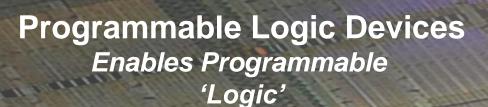

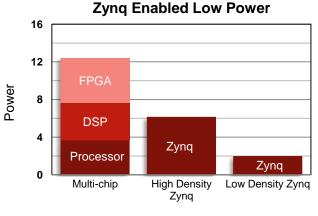

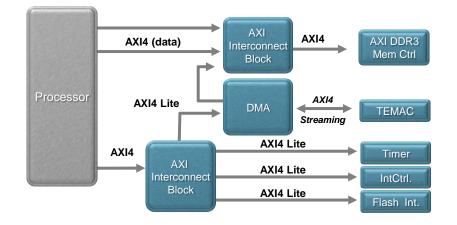

# The Zynq<sup>™</sup>-7000 Processor+FPGA SoC

#### > Complete ARM®-based Processing System

- Dual ARM Cortex<sup>™</sup>-A9 MPCore<sup>™</sup>, up to 1GHz

- Supports multiple operating systems

- Fully autonomous to the programmable logic

#### > Tightly Integrated Programmable Logic

- Used to extend processing system

- High performance AXI based interface

- Scalable density and performance: 30K-350K LCs

#### > Flexible Array of I/O

- Wide range of external multi-standard I/O

- High performance integrated serial transceivers

- Analog-to-Digital converter inputs

#### **Software & Hardware Programmable**

© Copyright 2012 Xilinx

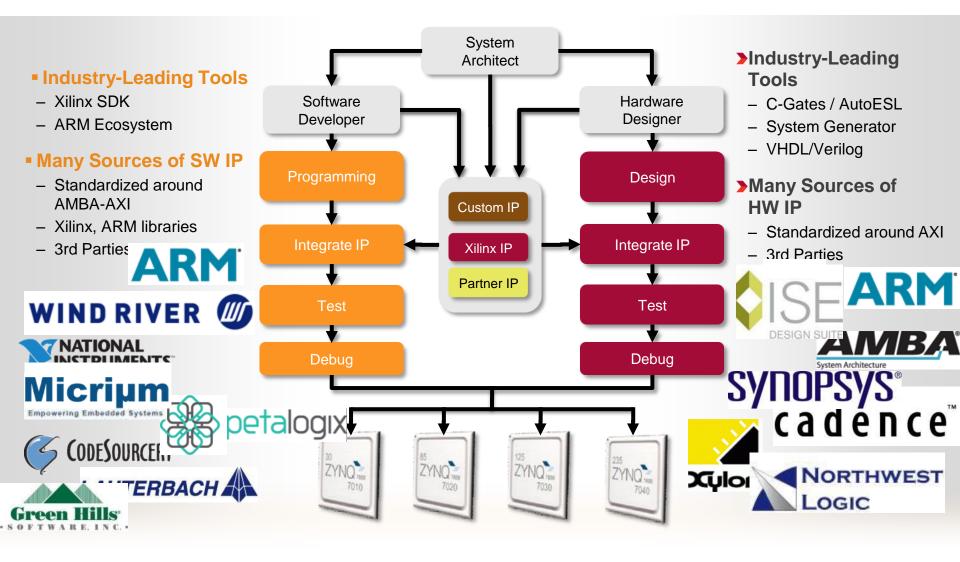

# **Embedded Design Flow Using Zynq-7000**

### Ground Breaking Capacity Gains at 28nm World's First 2 Million Logic Cell FPGA

> Over 2x capacity increase over Spartan-6 and Virtex-6 FPGAs

| Family               | Capacity Range        |  |

|----------------------|-----------------------|--|

| ARTIX.7              | 8K – <b>350K LCs</b>  |  |

| KINTEX. <sup>7</sup> | 70K – <b>480K LCs</b> |  |

| VIRTEX.7             | 330K – <b>2M LCs</b>  |  |

- SK 2M LCs; the widest capacity range offered in a single unified product family

- Larger densities enable higher performance

- More calculations/clock cycle by utilizing

Page parallelism inherent in FPGAs © Copyright 2012 Xilinx

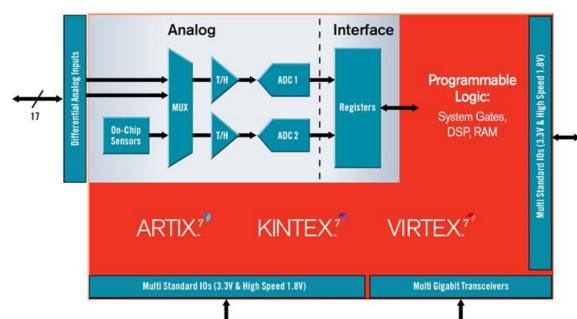

# **Agile Mixed-Signal Integration**

#### > Flexible general purpose analog interface

Integrated with all 7 series FPGAs and Zynq

#### Supports broad range of applications

- From simple monitoring to complex signal processing

- > Embedded temperature and supply sensors

- Enhance reliability, security and safety

#### Dual 12-bit 1Msps Analog-to-Digital Converters

- ADCs carry out 16-bit conversion with digital calibration

- ADC specified over full industrial range -40°C to +100°C

- DNL ±0.9 LSBs, INL ±2 LSBs, Gain Error ±0.4%, Offset ±4 LSBs

#### Dual Independent Track & Hold (T/H) Amplifiers

- Precise user control of sampling instant & simultaneous sampling

- Signal acquisition during conversion increases multiplexed throughput rate

- Track & Holds supports true differential sampling

- Track & Holds can be configured to support unipolor & bipolar signals

- On-chip Voltage Reference

- ±1% from -40°C to +100°C

- External reference input option

- On-Chip Thermal and Supply Sensors

- Temperature sensors with ±4°C error from -40°C to +100°C

- Power supply monitoring with ±1% error from -40°C to +100°C

- Automatic over temperature power down

- External Analog Input Channels

- One dedicated input channel for use with external analog multiplexer

- Up to 17 analog inputs supported using dual purpose digital IO

# Build better systems with fewer chips... faster

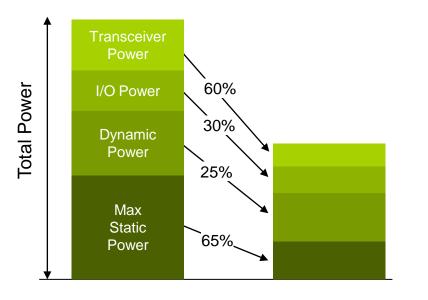

# **Total Power Reduction**

#### **50% FPGA Power Savings**

#### **5 Key FPGA Power Innovations**

- Optimized & Simpler HPL

- Re-architected Transceivers

- Multi-mode I/O Control

- Intelligent Clock Gating

- Voltage Scaling/Power Binning

#### 50-70% System-Level Power Savings

#### SSIT Enabled Low Power

# **Programmable Components**

- > Systems

- Logic

- Microprocessors

- **> I/O**

- >Analog/Mixed Signal

# It is ALL PROGRAMMABLE

# Enabling the Next Decade of ALL PROGRAMMABLE Devices

Accelerating Integration

up to 4X

1X

IP & System-centric integration with fast – verification

Vivado next generation design system

RTL to Bit-stream with iterative approach

> Fast, hierarchical and deterministic closure automation w/ ECO

Accelerating Implementation

1X

up to 4X

XILINX > ALL PROGRAMMABLE.

Algorithms

30-10

HP

Logic

ANS

Protocols

SI

10

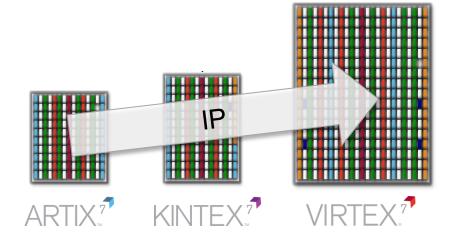

# **Maximizing Design Reuse**

#### **Architecture Enabled IP Portability**

#### Leveraging Standards for IP Reuse

Dramatically Reduce Time to Access, Reuse & Integrate World Class IP

**IEEE** P1735

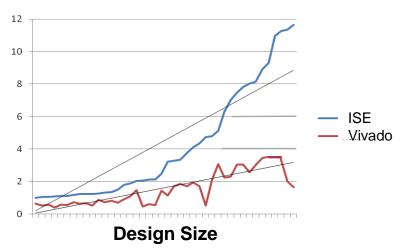

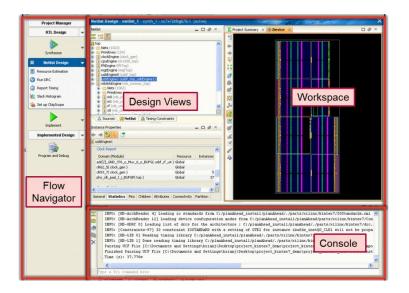

# Vivado: More Turns per Day, Ease-of-Use and Reuse

#### Vivado RTL->Bits

#### Vivado Run Time

Next Gen Architecture for Run-time, Memory Utilization & QoR

#### Vivado Design Environment

- Unified, streamlined, built for reuse

- U/I based on PlanAhead

- Simplified use models tailored to different user profiles

- Industry standard formats

- Hierarchical flows

- Easy IP packaging and reuse

© Copyright 2012 Xilinx

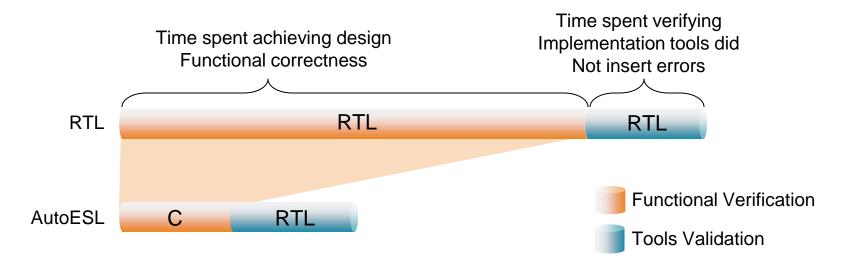

# More Turns per Day with High-Level Synthesis

#### 2-5X Step Function in Design Productivity vs RTL

#### **C-based High-Level Synthesis**

#### Optical flow video example

| Input                   | C Simulation Time | RTL Simulation Time | Improvement |

|-------------------------|-------------------|---------------------|-------------|

| 10 frames of video data | 10 seconds        | ~2 days*            | ~12,000X    |

\*RTL Simulations performed using ModelSim

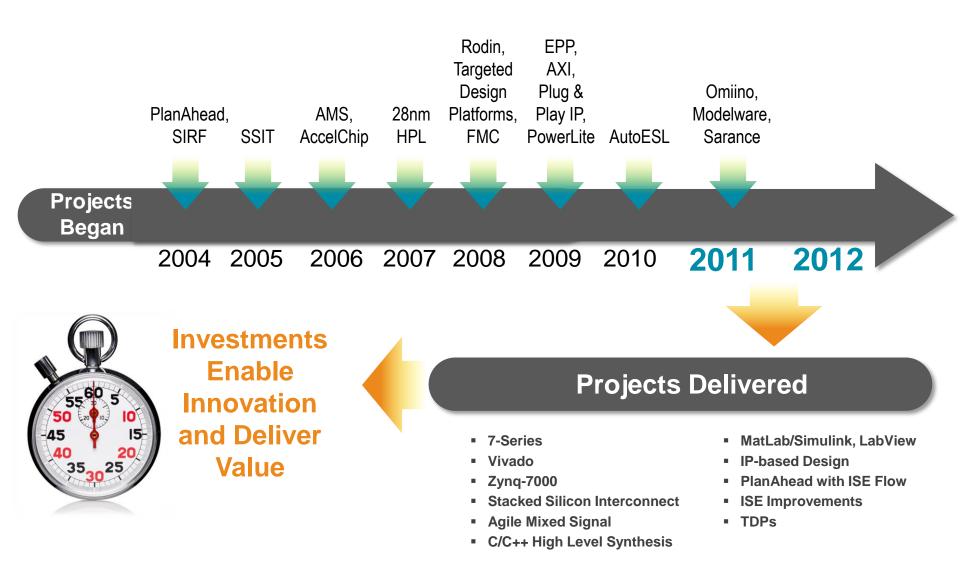

# **Recent Innovation and Investment Timeline**

# **Xilinx Technology Evolution**

Logic

FPGA

**ALL Programmable Devices Enables Programmable** Systems 'Integration'

AMBA

PGA

Algorithms

3D-1C

ARM FPGA

SerDe

MP

Logic

all 3DIC

SoC

FPGA

MS

Protocols

SerDes

AMS

AMS

XILINX > ALL PROGRAMMABLE.

SW

10

## The Road Ahead

- > Programmable logic is not only about programmable logic

- > We are still gaining tremendous benefit from scaling. And we have additional technologies we can use.

# ALL PROGRAMMABLE

ALL Programmable Electronic Systems

**ALL Programmable Technologies**

**ALL Programmable Devices**