# AMBIENT HARDWARE AND THE CASE FOR TRANSCODING MEDIA STREAMS Department of Electronics and Telecommu

Milica Orlandic, Kjetil Svarstad

Department of Electronics and Telecommunication, Norwegian University of Science and Technology, N-7491 Trondheim, Norway, Email: <u>orlandic@iet.ntnu.no</u> ΝΤΝΙ

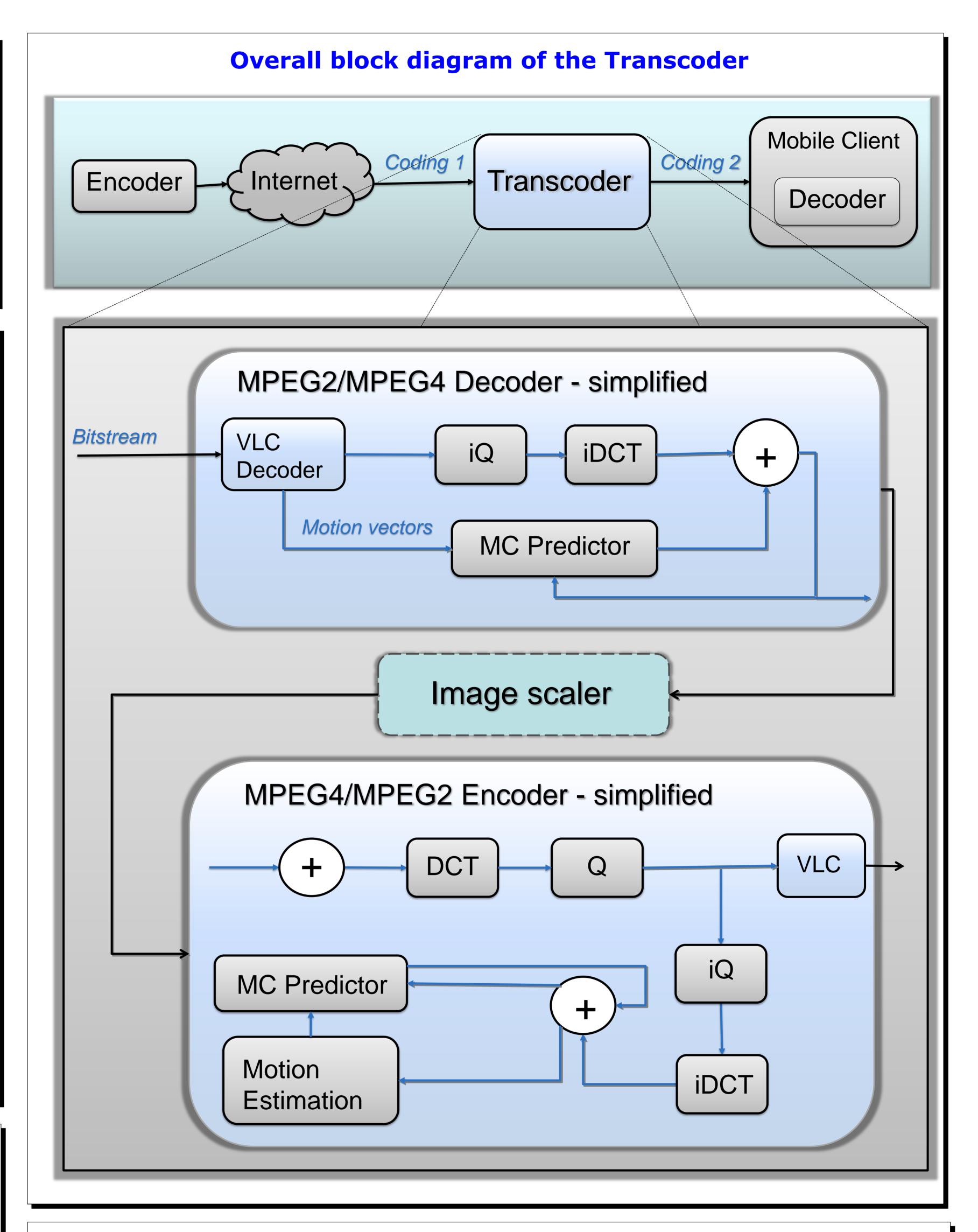

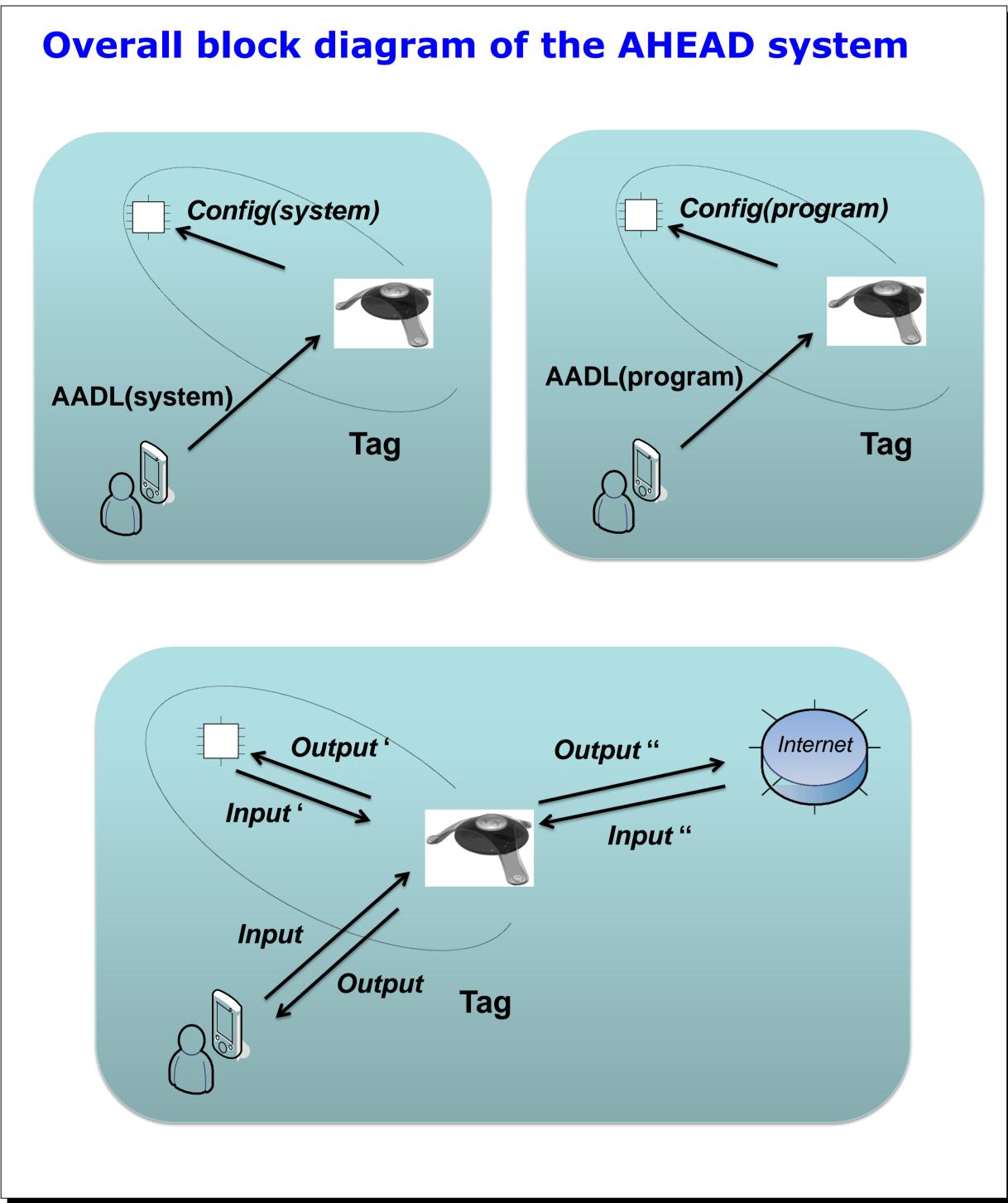

The objective of this project is to build a platform for autonomous, on-demand systems within video processing and other digital processing algorithms that require intensive computations and where mobile clients can save energy by off-loading computations to servers in the environment. Self-reconfiguration provides a necessary degree of flexibility for such systems.

## FRAMEWORK FOR PARTIAL SELF -RECONFIGURATION

The idea is to use an FPGA based server as an ondemand hardware accelerator enabling runtime reconfigurable modules to run as tasks that are fetched, placed and scheduled in time. These modules are provided on-demand from either the client or the network.

### **VIDEO PROCESSING ALGORITHMS AS RECONFIGURABLE MODULES**

The switching from Coding 1 to Coding 2 will be relevant and beneficent whenever the sum of transmission and decoding power on the mobile client becomes substantially smaller:

- $P_{Decode}(Coding \ 2) + P_{Rx}(Coding \ 2)$

- $< P_{Decode}(Coding 1) + P_{Rx}(Coding 1)$

#### CONCLUSION

The parts of the complex self-reconfigurable system have been implemented and tested. Intercommunication providing interrupt mechanism has been established. Further work on building a platform that will provide simplified manipulation of reconfigurability is planned. Complex systems such as video processing algorithms are intended to be built and tested on this platform.

#### References

- 1. J. Angermeier, C. Bobda, M. Majer and J. Teich. "Erlangen Slot Machine: An FPGA-Based Dynamically Reconfigurable Computing Platform", pp. 51-71, Springer, Heidelberg, February 2010M. Bellanger

- 2. C. Claus, W. Stechele, "AutoVision—Reconfigurable Hardware Acceleration for Video-Based Driver Assistance" In M. Platzner, J. Teich, & N. Wehn (Eds.), Dynamically Reconfigurable Systems (pp. 375- 394), Springer Netherlands, 2010

- 3. D. Koch, J. Torresen, "FPGASort: A High Performance Sorting Architecture Exploiting Runtime Reconfiguration on FPGAs for Large Problem Sorting Elements", pp. 45-54, FPGA'11, Monterey, California, USA, 2011

- 4. A. Koch "Adaptive Computing Systems and their Design Tools", pp. 117-138, Dynamically Reconfigurable Systems, 2010

- 5. J. Becker, M. Hiibner, M. Ullmann, "Run-Time FPGA Reconfiguration for Power/Cost Optimized Real-Time Systems", IFIP, Volume 200, VLSI-SOC: From Systems to Chips, eds. M. Glesner et al., (Boston:Springer), pp. 119-132

Presented at FPL 2012, Oslo, Norway, 29-31 August. Full paper published in the conference proceedings.