Architecture and FPGA Implementation of a 10.7 Gbit/s OTN Regenerator for Optical Communication Systems

Rodrigo Bernardo, Luis R. Monte, Eduardo Mobilon, Valentino Corso, Arley H. Salvador, Carolina G. Neves, Cleber A. Nakandakare, Daniele R. da Silva, Luis P. F. de Barros, Ronaldo F. da Silva

FPL2012 – Oslo, Norway, Aug. 29-31 2012

# Contents

- Motivation

- Design Architecture

- IP Block description

.

- Design Prototyping

- Resource usage

- FEC performance

- Conclusion

- Ongoing work

## **Motivation**

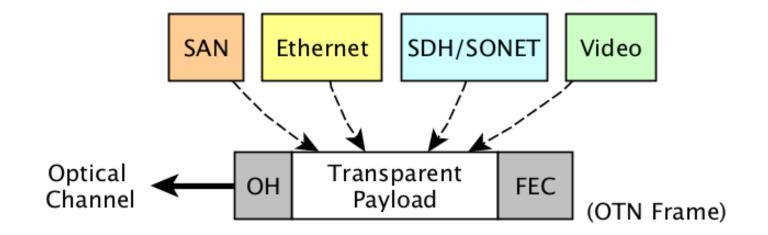

- OTN (Optical Transport Network)?

- Refers to networks using the ITU-T G.709 standard for WDM signals

- Provides transparent transport of different signals

## **Motivation**

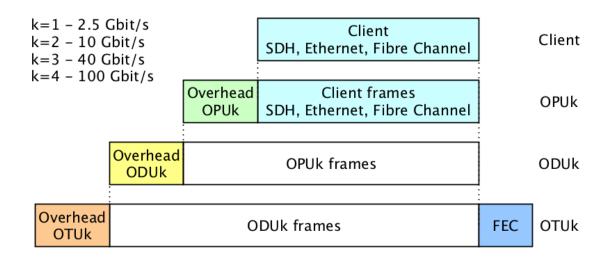

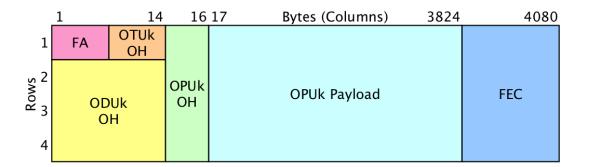

#### • OTN structure

• Hierarchically organized protocol

۲

## **Motivation**

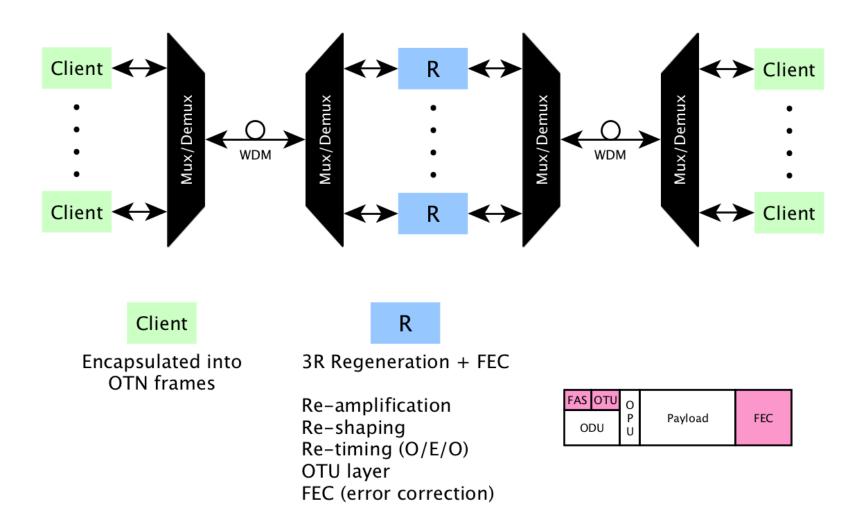

#### Signal regeneration

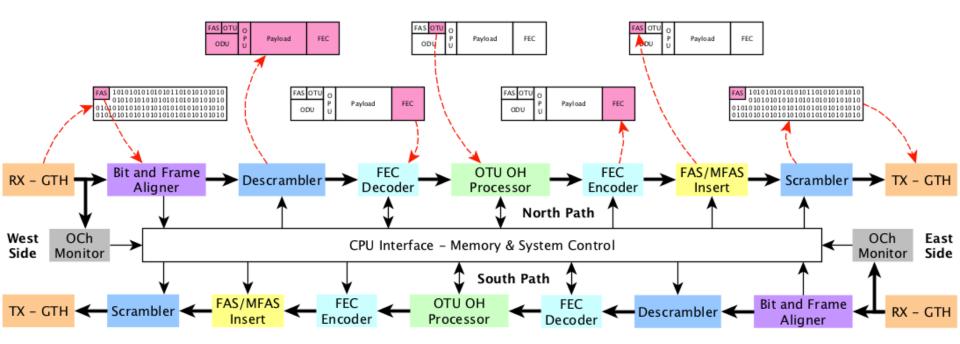

#### OTU2 Regenerator block diagram

- ITU-T G.709/G.798 standards

- Implemented in Xilinx Virtex-6 FPGA devices

- High Speed Transceivers

- They consist of Serializer/Deserializer devices that convert a high data rate serial signal into a parallel bus operating at lower speed

- They provide pre-emphasis, automatic gain control, loopback test, etc...

- In our design, the 10.7 Gbit/s OTN serial data stream (OTU2) is converted in a 64-bit bus, allowing data to be processed by the functional blocks at a much lower frequency of 167.33 MHz

- Transceivers + Optical Modules are responsible for the 3R regeneration (O/E/O)

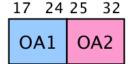

• Bit and Frame Aligner

| 1  | 8 | 9  | 16 | 17 | 24 | 25 | 32 | 33 | 40 | 41 | 48 | bits |

|----|---|----|----|----|----|----|----|----|----|----|----|------|

| OA | 1 | 0/ | A1 | OA | 1  | 0, | A2 | 0/ | 42 | 0/ | 42 |      |

• It searches the frame alignment pattern and aligns the 64-bit data word

• 02 operation modes: in-frame & out-of-frame

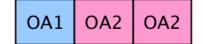

| OA1 | OA1 | OA1 | OA2 |

|-----|-----|-----|-----|

|-----|-----|-----|-----|

In out-of-frame mode, an FSM searches the elected 4-byte sequence in two steps:

OA1 = 0xF6OA2 = 0x28

In the first one, the transition is searched and it is aligned so that they occupy the 17<sup>th</sup> to 32<sup>nd</sup> position of the alignment pattern

| OA1 | OA1 |  |

|-----|-----|--|

|-----|-----|--|

The second step evaluates if the first two bytes of the pattern match the sequence

• In in-frame mode the aligner must confirm the sequence

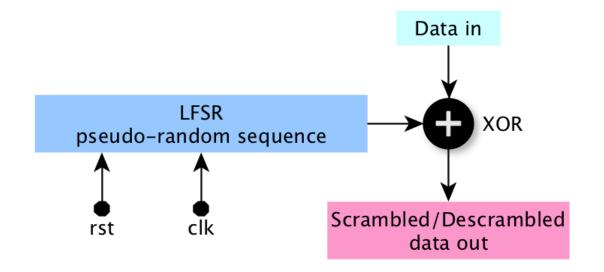

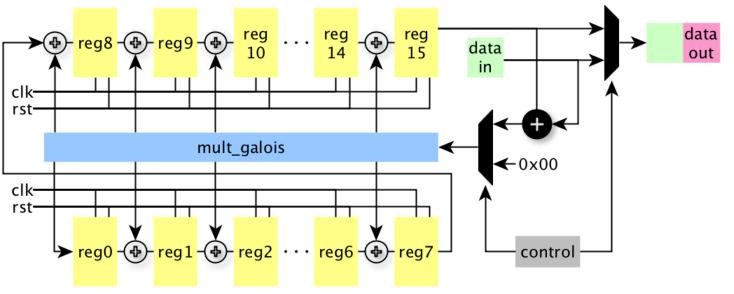

- Scrambler/Descrambler

- Linear Feedback Shift Register circuit

- Pseudo-random polynomial (1 + x<sup>1</sup> + x<sup>3</sup> + x<sup>12</sup> + x<sup>16</sup>) with a known sequence of 65,535 bits

- XOR operation

#### • Forward Error Correction RS(255,239)

The Encoder uses feedback shift registers for calculation and insertion of parity symbols, and also includes adders and multipliers that perform operations in accordance with the Galois algebra

| FA OTUk<br>OH |  |            |              |     |

|---------------|--|------------|--------------|-----|

| ODUk<br>OH    |  | OPUk<br>OH | OPUk Payload | FEC |

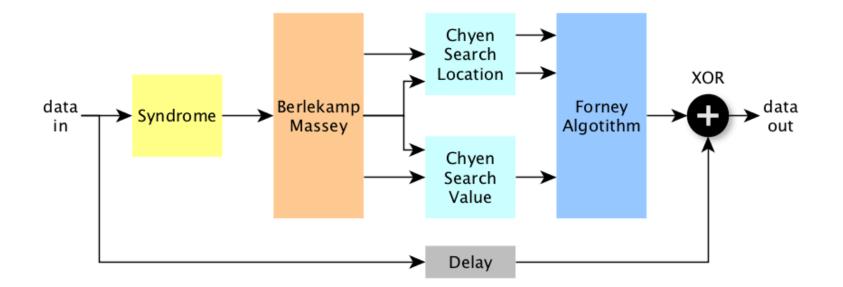

#### • Forward Error Correction RS(255,239)

- The Decoder has four functional blocks: Syndrome, Berlekamp Massey Algorithm, Chyen Search and Forney Algorithm

- The block also provides corrected bit counters for use in statistical analysis of the transmission path

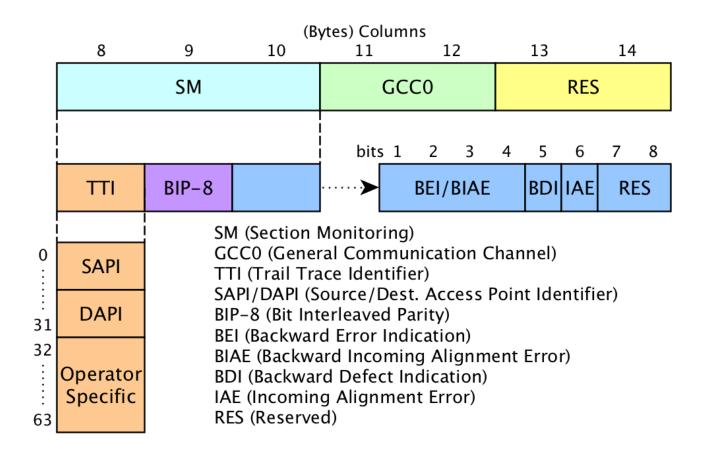

- OTU OH Processor

- OTU Layer monitoring

| FAS OT | U o    |         |     |

|--------|--------|---------|-----|

| ODU    | P<br>U | Payload | FEC |

.

#### • System control

• To emulate the CPU Interface, we have used Xilinx ChipScope as an I/O controller to manage the blocks

| VIO Console - DEV:1 MyDevice1 (XC6VHX565T) UNIT:0 MyVIO0 (VIO) | ¤ <sup>د</sup> ت۲ |

|----------------------------------------------------------------|-------------------|

| Bus/Signal                                                     | Value             |

| - descra_en                                                    |                   |

| -scra_en                                                       | 1                 |

| - rst_logic                                                    | 0                 |

| -loop_sel                                                      | 0                 |

| - enc_fec_en                                                   | 1                 |

| - dec_fec_en                                                   | 1                 |

| └ degm >>>>>>>DEFRAMER<<<<                                     | 0                 |

| ∽ bei                                                          | 0                 |

| bdi                                                            | •                 |

| biae                                                           | ۲                 |

| - piae                                                         | ۲                 |

| pbiae                                                          | •                 |

| - pn_ds                                                        | ۲                 |

| ∽ pf_ebc                                                       | 0                 |

| _pf_ds                                                         | ۲                 |

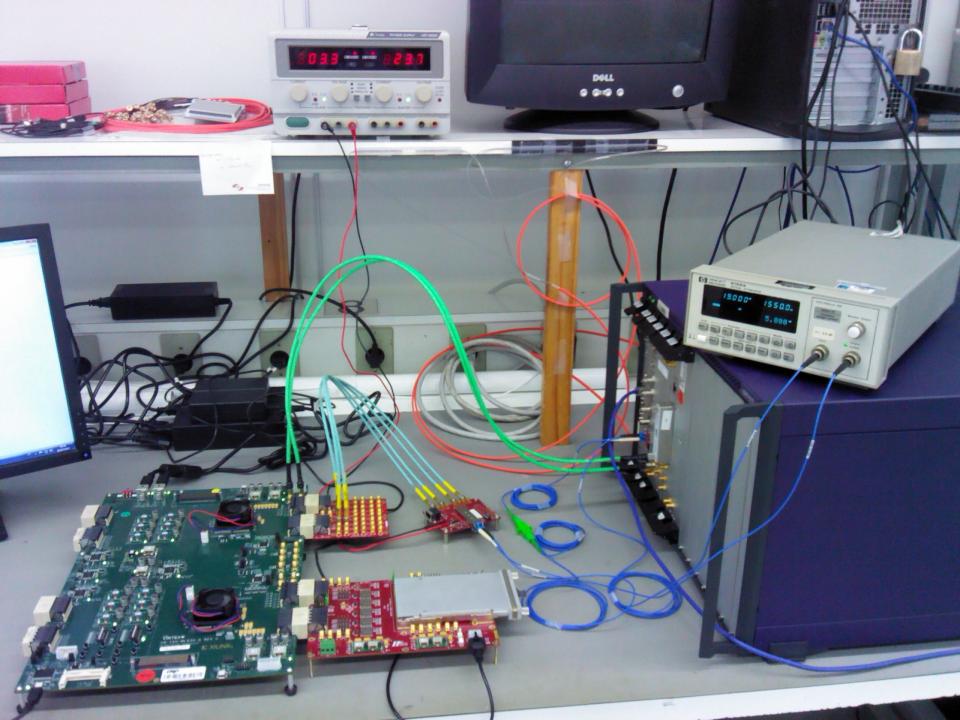

## **Design Prototyping**

#### • Resource usage

• The FEC Decoder block represents about 80% of the overall resource utilization of the complete design

| Blocks                         | Num   | ber of Slice | Registers   | Number of Slice LUTs |           |             |  |

|--------------------------------|-------|--------------|-------------|----------------------|-----------|-------------|--|

| DIUCKS                         | Used  | Available    | Utilization | Used                 | Available | Utilization |  |

| Bit & Frame<br>Aligner         | 268   | 708480       | 0.04%       | 892                  | 354240    | 0.25%       |  |

| Scrambler/<br>Descrambler      | 131   |              | 0.02%       | 164                  |           | 0.04%       |  |

| FEC<br>Encoder                 | 2872  |              | 0.40%       | 2848                 |           | 0.80%       |  |

| FEC<br>Decoder                 | 16458 |              | 2.32%       | 27693                |           | 7.82%       |  |

| Deframer<br>function           | 626   |              | 0.09%       | 587                  |           | 0.16%       |  |

| Framer<br>function             | 468   |              | 0.07%       | 198                  |           | 0.05%       |  |

| FAS/MFAS<br>Insert             | 65    |              | 0.01%       | 56                   |           | 0.01%       |  |

| Complete<br>OTN<br>Regenerator | 53869 | 708480       | 7.60%       | 81607                | 354240    | 23.04%      |  |

## **Design Prototyping**

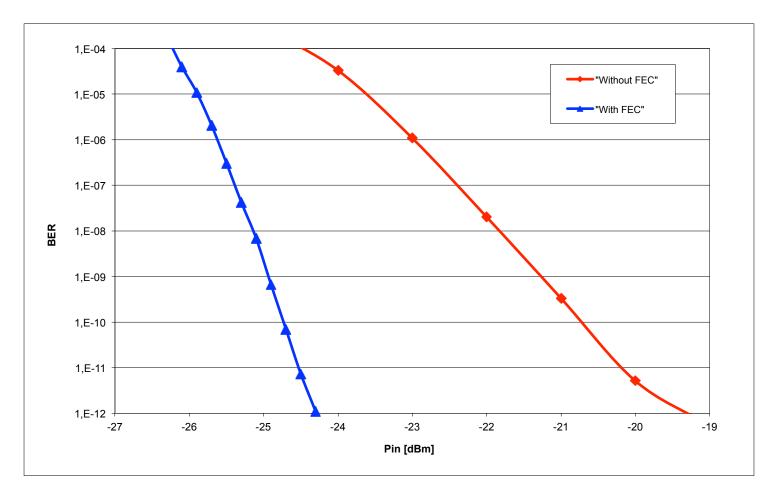

Sensibility @ 1.E-12 = -19.60 dBm / -24.55 dBm (FEC)

.

• Gain = 4.95 dB

# Conclusion

- Newest transceivers enable the implementation of highspeed telecommunication systems in a single FPGA, not requiring critical external components such as SerDes devices

- Even working with the state of the art in high operating frequency FPGAs, pipeline stages were necessary in the logic implementation to allow the timing requirements to be achieved

- Experimental results showed that the design is compliant with the standards

# **Ongoing Work**

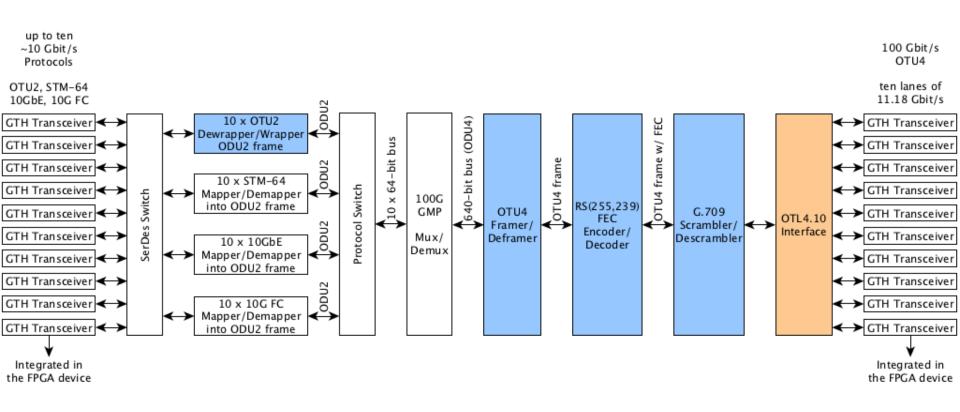

#### • 100G Muxponder

• The colored blocks are ready

# **Thank You!**

Rodrigo Bernardo, MSc

bernardo@cpqd.com.br +55 19 3705 7067

www.cpqd.com