## **Field-Programmable Logic and its Applications**

Oslo, Norway, Aug. 29-31, 2012

**Fault Detection and Avoidance of FPGA**

in Various Granularities

**Kumamoto University**

Kazuki Inoue, Yuki Nishitani, Motoki Amagasaki, Masahiro Iida, Morihiro Kuga, Toshinori Sueyoshi Kumamoto University, Japan

## **1. Introduction**

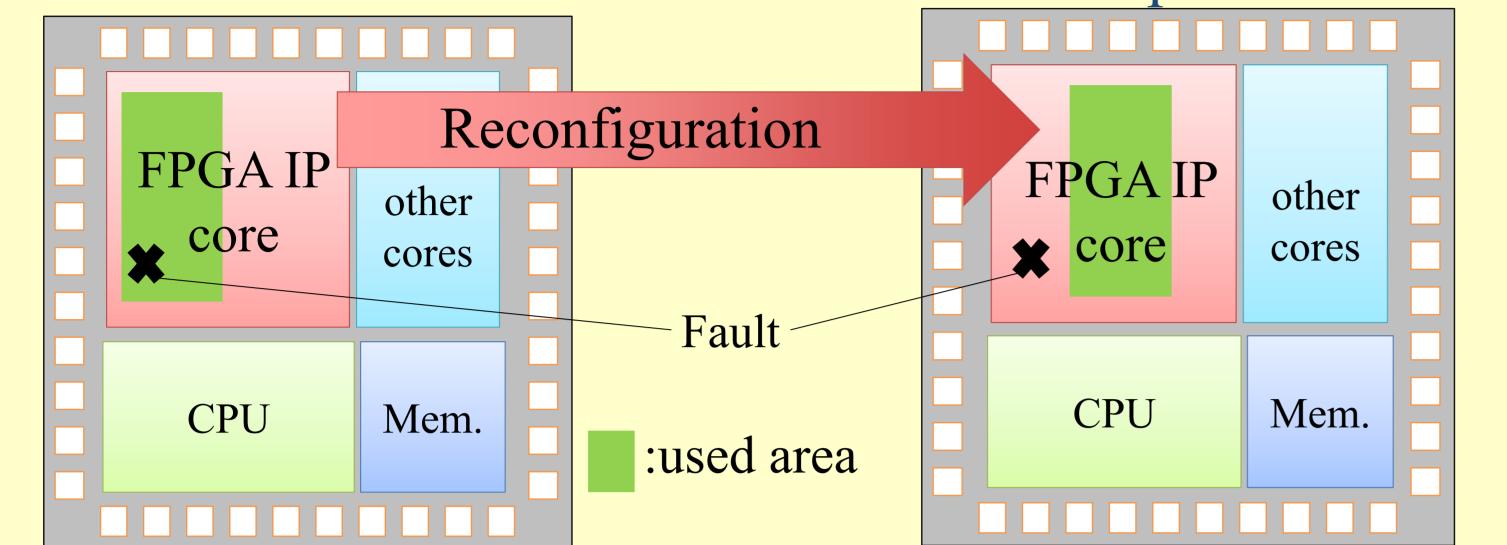

Fault Tolerant Technique with Reconfiguration

A Fault Tolerance is crucial for SoCs in dependable systems. We focus on the FPGA IP core to realize dependable SoCs.

# **<u>3. Fault Avoidance with CAD tools</u>**

Fault Avoidance in Placement phase

FPGA can easily recover from faults using reconfiguration.

### Key points of Fault Tolerant technique

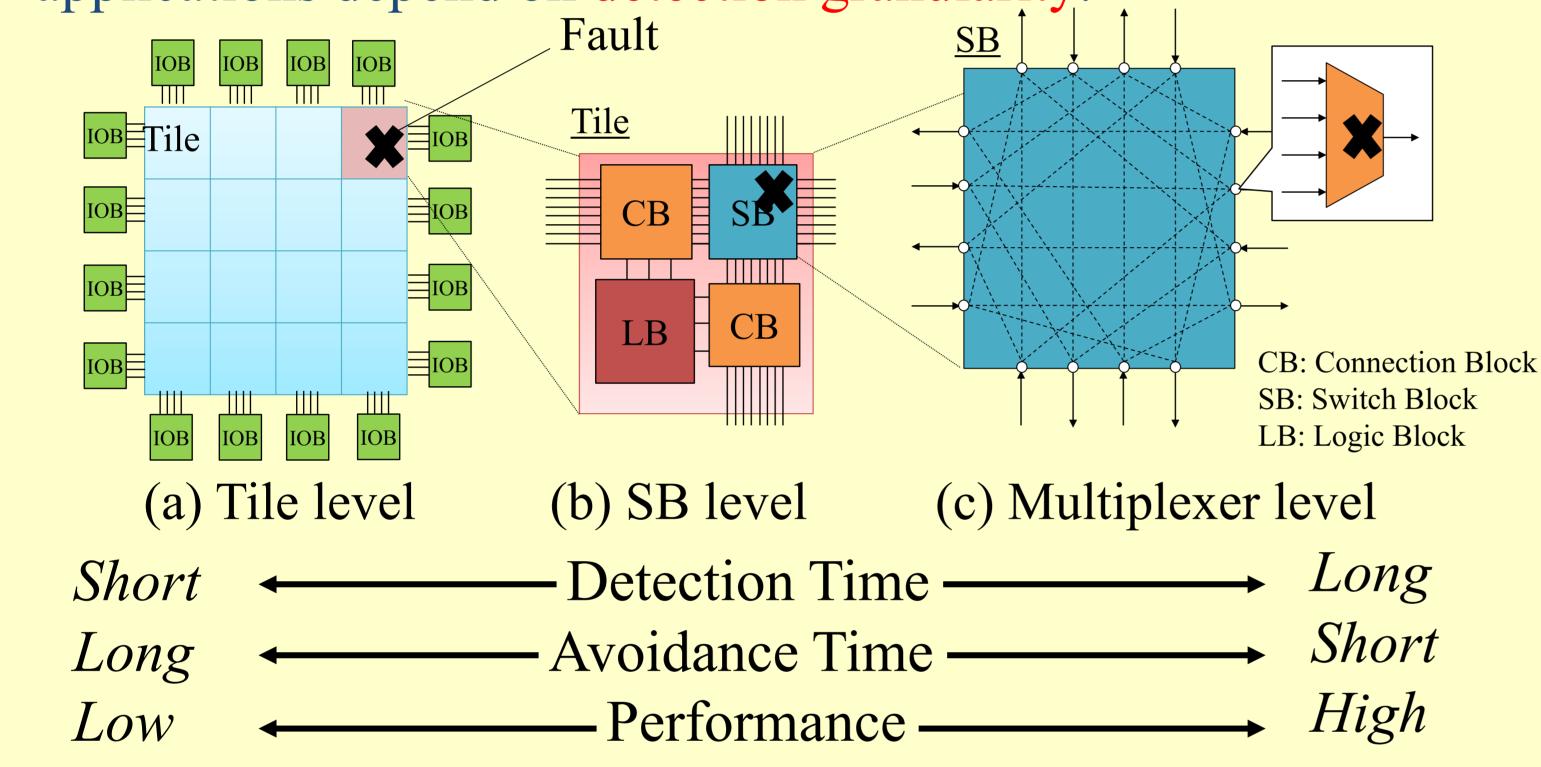

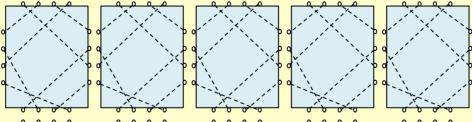

Recovery (detection and avoidance) time and performance of applications depend on detection granularity.

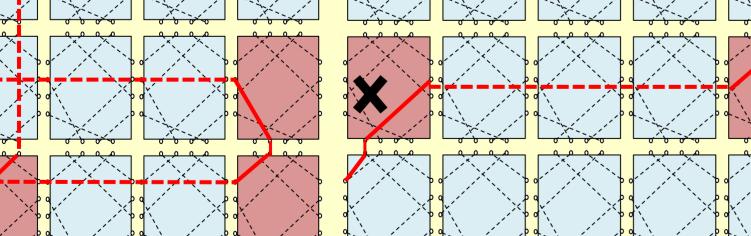

All signals cannot go through the fault Tile.

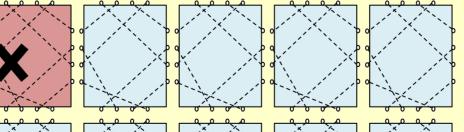

Multiplexer level avoidance

We propose fault detection and avoidance technique

for global interconnects in various granularities.

# **2. Fault Detection Technique**

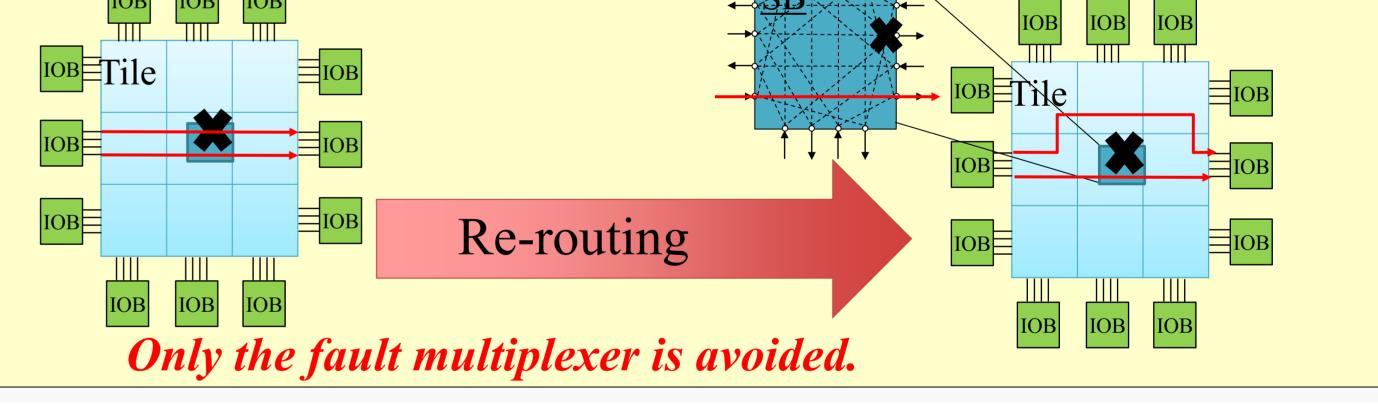

## Key Idea of fault-detection

### We combine several test paths to identify the fault points correctly.

SB(Switch Block) test signal

It's difficult to identify the fault point with one path.

## **4.Evaluation**

Ite

Lo

# 0

Co

₩d

| <b>Evaluation Conditions</b><br>Target Device |         | Target Fault                              |  |  |  |  |  |

|-----------------------------------------------|---------|-------------------------------------------|--|--|--|--|--|

| em                                            | value   | Stuck-at single fault at the SB           |  |  |  |  |  |

| rray size                                     | 16×16   | Detection Method                          |  |  |  |  |  |

| ogic block                                    | 4×6-LUT | Method(1): Test paths (a) and (b)         |  |  |  |  |  |

| nannel width                                  | 48      | Method(2): Test paths (b), (c), and (d)   |  |  |  |  |  |

| of I/O pins                                   | 128     |                                           |  |  |  |  |  |

| onfiguration bits                             | 136,896 | Avoidance Method                          |  |  |  |  |  |

| designed by 65 nm process technology          |         | Tile-level: Re-placement and re-routing   |  |  |  |  |  |

|                                               |         | Multiplexer (MUX) -level: Re-routing only |  |  |  |  |  |

# Evaluation Results Results of fault detection

Test path type-A

Test path type-B

De-B Combination of paths A and B.

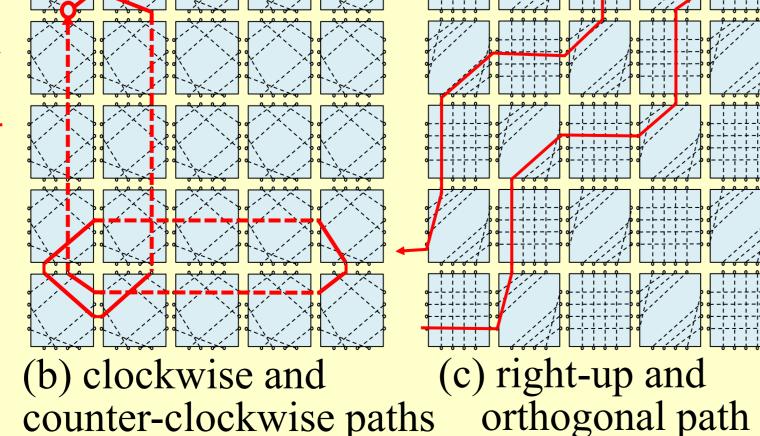

#### Proposed test paths

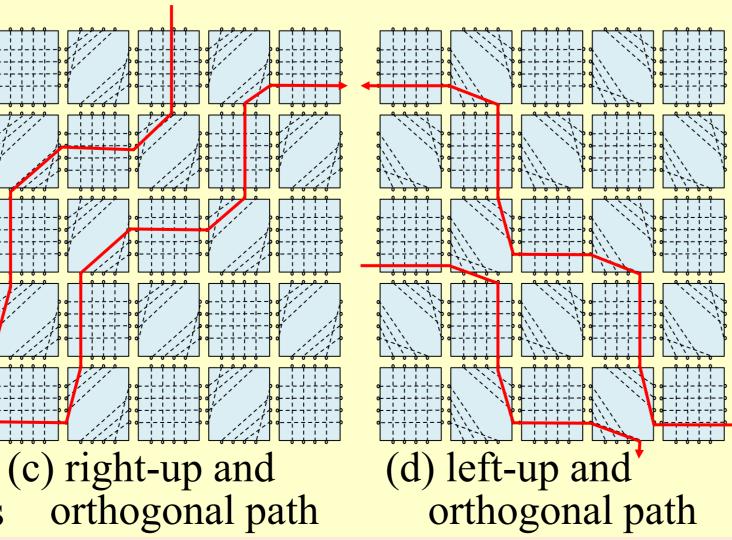

(a) orthogonal path

Test paths (a) and (b) were proposed in previous work. They achieved 100% fault coverage for interconnect testing.

(c) and (d) are newly prepared for fault diagnosis in this work.

| Ι                                                                                                                                      | <b>Detection method</b>                                                                                                                                 |                                 |             |       | Method  | (1)                         | Meth      | od (2) |      |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------|-------------|-------|---------|-----------------------------|-----------|--------|------|--|--|--|

| d                                                                                                                                      | letection time                                                                                                                                          | ection time (clock cycle)       |             |       |         | 992                         | 1,122,970 |        |      |  |  |  |

| #                                                                                                                                      | of fault tiles                                                                                                                                          | of fault tiles (worst/best)     |             |       |         | 4/4                         | 7/1       |        |      |  |  |  |

| #                                                                                                                                      | t of fault mult                                                                                                                                         | fault multiplexers (worst/best) |             |       |         | /12                         |           | 14/1   |      |  |  |  |

| The pa                                                                                                                                 | The paths of Method (2) detected the fault SB correctly                                                                                                 |                                 |             |       |         |                             |           |        |      |  |  |  |

| <i>with 40% additional time compared to Method(1)!!</i> <u>Circuit delays affected by fault-avoidance[ns]</u> <u>Avoidance time[s]</u> |                                                                                                                                                         |                                 |             |       |         |                             |           |        |      |  |  |  |

|                                                                                                                                        | No fault                                                                                                                                                | Met                             | thod (1) Mo |       | hod (2) | Cir                         | cuit      | Tile   | MUX  |  |  |  |

| avoid . lev                                                                                                                            | vel                                                                                                                                                     | Tile                            | MUX         | Tile  | MUX     | C62                         | 288       | 4.25   | 0.94 |  |  |  |

| C6288                                                                                                                                  | 96.7                                                                                                                                                    | N/A                             | 96.6        | 100.3 | 96.2    | core                        | dic       | 3.60   | 0.87 |  |  |  |

| cordic                                                                                                                                 | 103.4                                                                                                                                                   | N/A                             | 102.2       | 111.4 | 93.9    | ex4                         | p         | 3.28   | 0.38 |  |  |  |

| ex4p                                                                                                                                   | 46.4                                                                                                                                                    | N/A                             | 46.7        | 49.1  | 47.4    | N/A: Implementation failed. |           |        |      |  |  |  |

|                                                                                                                                        | # of fault-candidates Method (1) : 25 Tiles, 48 MUXs, Method (2): 2 Tiles, 2 MUXs.<br>MUX-level avoidance achieved high success ratio of implementation |                                 |             |       |         |                             |           |        |      |  |  |  |

and performance same as no fault FPGA in short avoidance time!!